Omfattande översikt över upp/nedräknare: kretsdesign och 74193 IC förklarade

I den intrikata världen av digital elektronik spelar räknare en viktig roll i sekventiell kretsdesign, vilket möjliggör exakt sammanfattning av digitala pulser i olika applikationer.Dessa grundläggande komponenter drivs av flip-flops (FFS) synkroniserade med klocksignaler (CLK), vilket säkerställer tillförlitlig temporär dataspårning och bearbetning.Oavsett om det fungerar som separata enheter eller som grundläggande delar av större system, har räknare blivit en nödvändig i digital design.Bland de olika typerna av räknare sticker upp/ner räknare ut för deras unika förmåga att räkna i båda riktningarna och erbjuder oöverträffad flexibilitet och effektivitet.I den här artikeln gräver vi in i mekanik, applikationer och betydelse av upp/ned -räknare, med en strålkastare på den mångsidiga 74193 IC.Genom att utforska deras roll i faktiska system och digitala innovationer strävar vi efter att ge en omfattande guide för dig.Katalog

Förstå upp/ner -räknaren

Upp/ner räknare erbjuder en komplicerad räkningsmetod, vilket möjliggör dubbelriktningsoperationer baserade på särskilda styrsignaler.Dessa räknare finns i applikationer där räkning upp och ner båda behövs, såsom ses i TTL -teknologier - som 74LS190 och 74LS191 - som adeptly switch counting -lägen som svar på deras ingångsdirektiv.

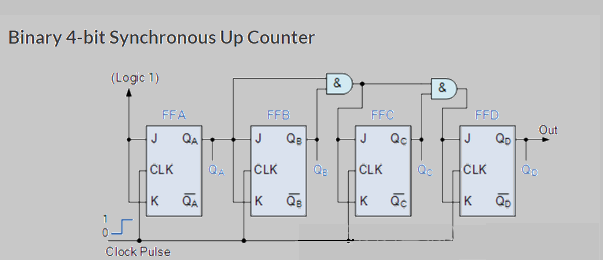

4-bitars binär upp/ner räknaren

Den 4-bitars räknaren visar binär räkning, skickligt navigerar från 0000 till 1111 och looping cykliskt.Klockpulser driver den ökande mekanismen över ett 0-15-intervall, med varje fästing som metodiskt uppmanar ett efterföljande tillstånd.

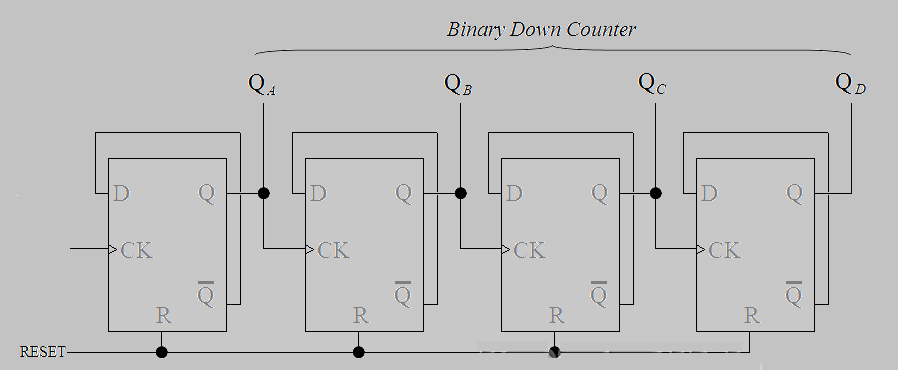

Däremot förlitar sig den minskande processen, som växlar från 1111 till 0000, på fyra flip-flops av D-typ aktiverad av klockkanter.Den innovativa användningen av inverterade feedbackmekanismer uppnår ett harmoniskt samspel av resultat, vilket belyser både kreativitet och precision.

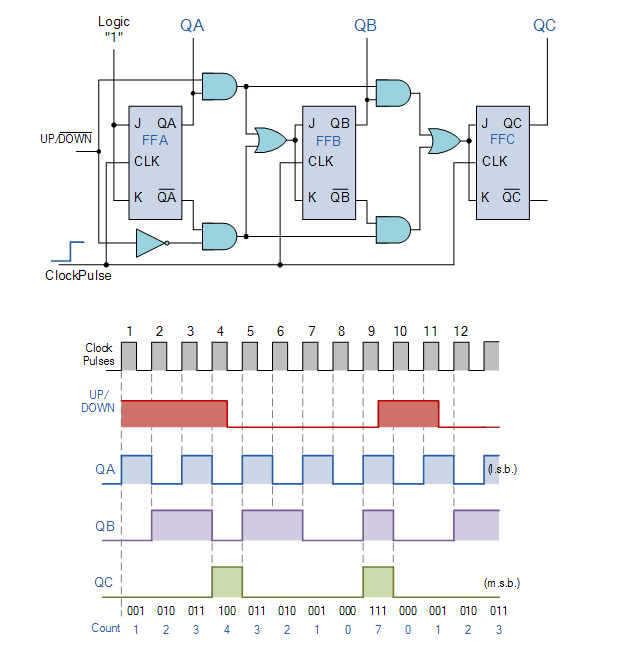

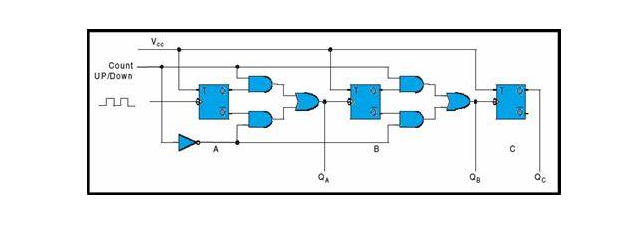

Synkron 3-bitars upp/ner räknaren

Den 3-bitars synkrona räknaren, som använder JK-flip-flops, exemplifierar ett effektivt tillvägagångssätt för att räkna från 0 (000) till 7 (111) och tillbaka.Dess synkrona design möjliggör förfinad kontroll över räkningsprocessen, där varje tillståndsövergång samordnas av exakta ingångskommandon.Denna funktion förbättrar noggrannheten i uppåtgående från 0 till 7, samtidigt som han hanterar nedräkning från 7 tillbaka till 0.

Designa en upp/ner motkrets

Den 3-bitars räknarkretsen står som ett viktigt element i digital design och serverar olika räkning och tidsändamål.Det använder konsekvent flip-flops (FFS) för att bestämma räknarens riktning-avslappnad eller fallande.

I uppräkningsläget är varje FF i linje med en klockinmatning från föregående FF: s utgång (q), vilket leder kretsen i en ordnad uppstigning genom binära tillstånd från 000 till 111. Denna sekvens finner ofta fördel i applikationer som kräver exakt tidpunktKontroll, inklusive digitala klockor och kalkylatorer där noggrannhet framkallar tillfredsställelse och tillförlitlighet.

Att byta till nedräkningsläge kräver ett smart tillvägagångssätt och engagerar Flip-Flops inverse utgångar.Avvikande från en enkel framåt mars, omdirigerar denna konfiguration varje FF: s klockingång för att ta emot signaler från komplementet till föregående FF: s Q -utgång.Följaktligen räknas kretsen i omvänd riktning, från binär 111 tillbaka till 000. Sådan anpassningsbar funktion, visar sig huvudsakligen tilltalande när man utformar reversibla räknare för backtracking i system som digitala odometrar och dekrementtimers - det subtila nöjet att röra sig så smidigt som framåt kan inte förbises.

Mekanik för upp/ned -räknaren

Funktionen för upp/ned -räknaren förlitar sig på en kontrollinmatning som definierar dess driftsläge och dikterar om räkningen kommer att stiga upp eller stiga ner.Kärnan i dess operation ligger i den sömlösa synkroniseringen mellan utgången från flip-flops (FFS) och styrsignaler som påverkar efterföljande FF: er.I applikationer kan till och med den minsta avvikelsen från perfekt timing leda till räkningsfel, vilket betonar hur dynamiskt det är att samordna signaltiden exakt.

• Uppräkningsläge

|

Ange |

QC |

QB |

QA |

|

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

|

2 |

0 |

1 |

0 |

|

3 |

0 |

1 |

1 |

|

4 |

1 |

0 |

0 |

|

5 |

1 |

0 |

1 |

|

6 |

1 |

1 |

0 |

|

7 |

1 |

1 |

1 |

• nedräkningsläge

|

Ange |

QC |

QB |

QA |

|

7 |

1 |

1 |

1 |

|

6 |

1 |

1 |

0 |

|

5 |

1 |

0 |

1 |

|

4 |

1 |

0 |

0 |

|

3 |

0 |

1 |

1 |

|

2 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

|

0 |

0 |

0 |

0 |

I en typisk konfiguration lagrar tre flip-flops ett 3-bitars digitalt värde, vilket möjliggör ett binärt antal som sträcker sig från 0 till 7. Du kan ofta möta utmaningar som upprätthåller tillförlitligheten i lagrade värden, särskilt när du handlar om miljöer med elektriskt brus eller störning.För att hantera dessa utmaningar används ofta ytterligare synkroniserings- eller filtreringstekniker, vilket säkerställer att data bevaras med integritet under övergångar.

Logikgrindar påverkar avsevärt hur dessa signaler riktas, vilket säkerställer att räknaren uppfyller dess operativa behov.De hanterar flödet för att säkerställa att endast ett tillstånd - antingen ökar eller minskar - är aktiva när som helst.Avancerade kretsar kan innehålla programmerbar logik, erbjuda förbättrad anpassningsförmåga och dynamiska justeringar.Detta introducerar en spännande aspekt: att utforma räknare med framsyn för framtida skalbarhet kan bredda deras användbarhet avsevärt.

Raffinerande klockpulsdynamik med en upp/ner -räknare

En upp/ner-räknare omvandlar tillstånd genom att justera utgångar i flip-flop (FF) som svar på klockpulsförändringar.

• I uppräkningsscenariot: Anslut den initiala flip-flop till logik 0, vilket får det att växla på fallande klockkanter, vilket förbättrar synkroniseringen med systemmål för sömlöst flöde.Tankar som härrör från digitala kretsdesignupplevelser tyder på att balansering av dessa växlingsåtgärder kan minska falska triggers och därmed öka tillförlitligheten över tid.

Nedräkning och harmonisk statlig övergång

• I nedräkningsläget: Anslut till Logic 1 för att göra det möjligt för alla flip-flops att växla, vilket leder till en smidig minskning från högre tillstånd.Denna metod kan jämföras med en försiktig avlindning av en fjäder, där precision och tidpunkt säkerställer en minimal mekanisk stam under återgången till baslinjen.Detta arrangemang underlättar en gradvis minskning tills en återställningssekvens uppmanas.

Effektiv återställning av cykel och konsistens

Rutinmässiga återställningar förekommer var åtta klockcykler, vilket säkerställer konsekvent drift.Ramverket på åtta cykel ger en definierad fas för varje tillståndsskift, vilket säkerställer att varje fas slutförs effektivt innan nästa börjar.Feedback från praktiska applikationer antyder att dessa periodiska återställningar förhindrar ackumulering av fel, vilket förstärker driftsjämvikt.

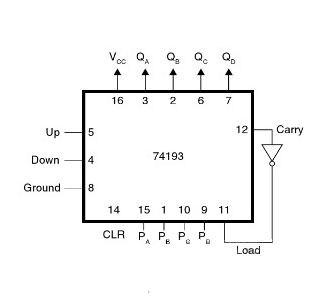

74193 upp/ner mot IC -översikt

De 74193 Integrerad krets, känd som en 4-bitars synkron binär räknare, hanterar Adeptly både uppåt och nedåt räkningsfunktioner.Dess förmåga att hantera räkningssekvenser upp till ett modulo på 16 lämpar sig för ett brett utbud av digitala applikationer.Denna IC är unikt utformad med terminaler specifikt för upp- och nedräkning, tillsammans med en masteråterställning och lastingång, vilket ger lätthet att konfigurera det ursprungliga tillståndet enligt olika behov.

Arkitekturen för 74193 IC stöder enkel riktningsräkning.I digitala enheter förbättrar valet mellan uppåt och nedåtgående räkningens anpassningsförmåga.Varje räkningoperation är exakt i linje med klockpulsen, vilket gör det till ett tillförlitligt val för komplicerade system där tidpunkten är av väsentligheten.För dig kan denna synkronisering vara en strategisk faktor för att säkerställa konsekvent sekvensutförande.

En nyckelfunktion i denna IC är masteråterställningen, som möjliggör omedelbar återställning av alla bitar - en funktion som ofta används under start eller vid korrigeringsfel.Dessutom ökar lastinmatningen dess användbarhet genom att göra det möjligt för dig att ställa in förutbestämda initiala räkningar, vilket tillåter en viss personalisering som krävs i olika digitala sammanhang.Sådan personalisering blir grundläggande i scenarier där enheter genomgår regelbunden initialisering eller kräver särskild hantering under avbrott.

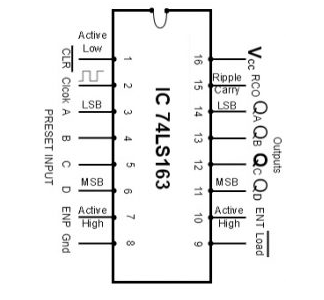

Stiftkonfiguration

|

Stiftnummer |

Stiftnamn |

Beskrivning |

|

Stift 1 |

Clr |

En aktiv-låg återställning ingång. |

|

Stift 2 |

Klk |

En klockingångssignal. |

|

Stift 3 |

A (LSB) |

Datainställningsinmatning. |

|

Stift 4 |

B |

Datainställningsinmatning. |

|

Stift 5 |

C |

Datainställningsinmatning. |

|

Stift 6 |

D (MSB) |

Datainställningsinmatning. |

|

Stift 7 |

Enp |

En aktiv hög ingång märkt ENP. |

|

Stift 8 |

Gard |

Markstift. |

|

Stift 9 |

Ladda |

En aktiv-låg datalastingång. |

|

Stift 10 |

Ent |

En aktiv hög ingång märkt ENT. |

|

Stift 11 |

QD (MSB) |

Flip-flop-utgång. |

|

Stift 12 |

QC |

Flip-flop-utgång. |

|

Stift 13 |

QB |

Flip-flop-utgång. |

|

Stift 14 |

QA (LSB) |

Flip-flop-utgång. |

|

Stift 15 |

Rco |

Rippel bär utgångsövergången från 0 till 1. |

|

Stift 16 |

Vcc |

Effektinmatningsstift. |

Drag

|

Särdrag |

Beskrivning |

|

CLK -frekvens |

Fungerar med en CLK -frekvens på 32 MHz. |

|

Kraftanvändning |

Kraftanvändning är täckt vid 93 MW. |

|

Mottyp |

Funktioner som en 4-bitars Modulo-16 upp/ner-räknare. |

|

Förinställda ingångar |

Levereras med tillgängliga förinställda ingångar. |

|

Programmering |

Har synkron programmering. |

|

Rippelbär |

Har en intern krusning för effektiv räkning. |

|

Bärning |

Erbjuder en bärutgång som är lämplig för n-bit kaskadering. |

|

Förökningstid |

Har en förökningstid på 14 ns. |

Bygga en upp/ner -räknare med IC 74193

Den komplexa 74193 IC, som är erkänd för sina anpassningsbara räkningsfunktioner, är en värdefull komponent i digitala system för att möjliggöra mångsidiga upp/nedräkningsuppgifter.I kretslayouten är PIN-16 ansluten till VCC för att ge IC med driftskraft.De tydliga stiften är jordade strategiskt, som verkar för att återställa räknaren vid behov, vilket hjälper till att upprätthålla systemets tillförlitlighet och prestanda.

Binära data kommer in i IC genom stift PA, PB, PC och PD.Motsvarande binära utgångar kan nås på QA, QB, QC och QD, vilket levererar bearbetade räkningar som mestadels är fördelaktiga för uppgifter som tidskretsar och frekvensdelare som kräver hög precision.

Räkningsriktningen, vare sig ökning eller minskning, styrs genom specialiserade klockingångar.Denna kapacitet låter dig dynamiskt justera räkningssekvensen för IC och förbättra dess flexibilitet i olika applikationer.När man använder IC i praktiska scenarier är det dominerande att noggrant forma klockpulsen och ta itu med brusproblem för att undvika felaktiga räkningar, vilket säkerställer att kretsen fungerar pålitligt.

Jämförande analys av UP -räknare och nedre räknare

|

Uppdisk |

Nedför disk |

|

UP -räknaren räknar från '0' till sin maximala gräns |

Ned räknaren börjar från sitt toppvärde och går ner

till '0' |

|

Det räknar händelser i en stigande sekvens |

Det räknar händelser i en fallande sekvens |

Styrkor och begränsningar av upp/ned räknare

Styrkor

Upp/ner räknare ger olika fördelar, särskilt i världen av Integrering i höghastighetssystem.Deras enkla flip-flop-struktur hjälper till att enkelt anslutning, vilket ofta leder till kostnadseffektiva alternativ för digitala enheter där minimering av komplexitet är en prioritering. Förmågan att räkna i båda riktningarna - uppåt och nedåt - adds mångsidighet, vilket visar sig vara fördelaktigt i applikationer som digitala klockor eller evenemangsräknare där dubbelriktning är önskvärt. Dessutom lyser deras funktionalitet i testsystem som används för att bekräfta logiska signaler.Hands-on-applikationer uppskattar deras okomplicerad design, som säkerställer enklare felsökning och underhåll och erbjuder en anmärkningsvärd fördel för dig med fokus på problemlösning och optimeringsuppgifter.

Begränsningar

Trots styrkorna visar upp/ned -räknare särskilda begränsningar, särskilt när det gäller precision vid förhöjda frekvenser. När operativa hastigheter stiger kan de möta felaktigheter och utgöra utmaningar i system som prioriterar hög tillförlitlighet. Dessa felaktigheter härstammar ofta från beroende av extern klocksynkronisering, vilket specifikt kan kräver kompletterande flip-flop-kretsar.Sådana krav kan Öka kretskomplexiteten och införa potentiella förseningar i tidpunkten.Dessutom, när man hanterar intrikata bitsystem, Eventuella förseningar som är förknippade med räknarna kan förvärra, påverkar den övergripande systemprestanda.Följaktligen kan du ofta utforska alternativa lösningar eller ytterligare komponenter för att mildra dessa effekter och basera sina strategier på förbättrade synkroniseringstekniker.Att navigera i dessa kompromisser kräver en tankeväckande utvärdering av systembehov och hur sådana element kan påverka prestanda, ofta styr dig mot strategiska designförbättringar anpassade till specifika applikationskrav.

Användning av upp/ned räknare

Auto-omvänd räknare

I världen av systemteknik som kräver noggrann kontroll introducerar upp/nedräknare en användbar funktion: den automatiska justeringen av räkningsriktningen vid fastställda gränser.Denna anpassningsförmåga stöder en felfri övergång mellan framåt och bakåträkning.En sådan funktion blir särskilt värderad i automatiserade miljöer där spårning av rörelse i båda riktningarna påverkar kraftigt operationell effektivitet.Industriell robotik, till exempel, utnyttjar detta attribut för att säkerställa noggrannhet efter att ha nått sina rörelsesgränser.

Klockdelare

Inom digitala elektroniska system bidrar upp/ned -räknare avsevärt till tillverkningen av klockdelare, som skickligt modulerar frekvensen av klocksignaler.Denna modulering hjälper till att konstruera tidssignaler som är nyckeln för att driva olika komponenter vid olika frekvenser inom ett integrerat system.Genom att erbjuda klockor med olika hastigheter spelar dessa räknare en viktig roll i synkronisering av olika processer och därmed tillfredsställer unika systembehov.

Parkeringssystem

I stadsutrymmen som kvävs med trafik levererar upp/nedräknare dynamiska lösningar genom parkeringshanteringssystem.Genom att metodiskt öka räkningen med varje fordons inträde och minska det vid utgången ger dessa räknare snabba uppdateringar av tillgängliga parkeringsplatser.Denna faktiska spårningsmekanism stöder effektiv användning av parkeringsinfrastruktur samtidigt som du berikar din upplevelse.

Frekvenspartitionering

För uppgifter som involverar frekvenspartitionering i kommunikationsnätverk visar upp/ned -räknare vara exceptionellt fördelaktiga på grund av deras låga brus och minskade kraftförbrukning.Dessa räknare hjälper till i den noggranna uppdelningen och hanteringen av frekvenser, vilket möjliggör boende för flera kanaler i ett nätverk.I miljöer med omfattande signalbehandling garanterar användningen av sådana räknare minimal störning, upprätthåller integriteten och kvaliteten på kommunikationssignaler.

Asynkron dekadalräkning

Upp/ner räknare möjliggör asynkron decadalräkning, som används för applikationer där verksamheten inträffar oberoende av globala klockor.I asynkrona system ger dessa räknare ett pålitligt tillvägagångssätt för att uppnå bas-10-räkning, utmärker sig i anpassningsförmåga utan att förlora precision.Deras användbarhet lyser i system som arbetar över olika förhållanden och justerar smidigt utan att offra noggrannhet.

Slutsats

Den här artikeln gräver in i den intrikata designen och operativa aspekterna av upp/ned -räknaren, med fokus på 74193 IC.Känd för sina dubbla räkningsfunktioner - både stigande och fallande - har det olika tillämpningar, från sofistikerade parkeringssystem till intrikata frekvensuppdelning.När tekniska landskap förändras kan en djup förståelse av dessa komponenter driva innovation och öka effektiviteten.Upp/ned -räknarens verktyg sträcker sig utöver konventionella applikationer och vågar sig in i automatiserade system där exakta räkningsmekanismer förbättrar effektiviteten.Till exempel, i dynamiska trafikhanteringslösningar, spelar sådana räknare en viktig roll genom att integrera faktiska data för att optimera flödet.Att utnyttja enhetens mångsidighet gör det möjligt att möta utmaningar i olika sektorer med anpassade strategier.Från branschspecifika insikter kan den exakta implementeringen av dessa räknare avsevärt öka systemprestanda.

Om oss

ALLELCO LIMITED

Läs mer

Snabb förfrågan

Skicka en förfrågan, vi svarar omedelbart.

Vanliga frågor [FAQ]

1. Vad är teorin bakom en 8-bitars upp/ner-räknare?

En 8-bitars upp/ner-räknare hanterar en 8-bitars digital signal, vilket visar sig vara användbar i designarkitekturer som digital-till-analogkonverterare (DAC) och avkodare.Den har ofta LED -skärmar och involverar konfiguration genom åtta stift.Räknarens anpassningsförmåga framhävs genom att utforska digital signalbehandlingsintrikatser, användbara i både sofistikerade beräkningssystem och enklare enheter.Implementering av dessa räknare kräver vanligtvis noggrann uppmärksamhet på signalintegritet och inställningsnyanser.

2. Hur använder en upp/ner-räknare JK-flip-flops?

Denna 4-bitars räknare använder synkron operation med JK-flip-flops för att ändra räkning riktning baserat på det logiska tillståndet för upp/ner-ingången.Den reagerar på klockpulser, medan den möjliggörande ingången fungerar som en aktiv kontrollmekanism.Du kan utnyttja denna design för att säkerställa tillförlitlig timing och sekventiell prestanda i olika applikationer, vilket illustrerar effektiviteten hos synkrona digitala system.Att förstå dessa sofistikerade system kan erbjuda bredare insikter i digitala kretsar och inspirera innovativa logikdesignlösningar.

3. Vad skiljer 74192 -räknaren från 74193 -räknaren?

74192 fungerar som en BCD-decennium, och 74193 fungerar som en 4-bitars synkron binär räknare.Båda är skräddarsydda för olika roller inom digital elektronik.Att erkänna varje räknets distinkta funktioner hjälper till att välja lämpliga komponenter för synkrona räkningsuppgifter.Sådana utformningsbeslut kan påverka operativ effektivitet och sammanhållning väsentligt i komplexa kretsar, vilket erbjuder värdefulla perspektiv för att optimera integrerad systemdesign.

4. Hur definieras en 2-bitars upp/ner-räknare?

En 2-bitars upp/ned-räknare korsar en enkel binär sekvens från 0 till 3, som fungerar i både uppåt och nedåt beställningar.Denna operation belyser de ultimata logiska principerna och enkelheten som möjligt i digitala system.Sådana räknare fungerar som tydliga exempel på binär aritmetik och erbjuder praktiska inlärningsupplevelser som förbättrar utbildningsmodellerna och underlättar enhetstestning och därmed fördjupar förståelsen för binära operationer.

5. Hur fungerar CD4029 -motståndet?

CD4029 -räknaren fungerar flexibelt, kapabel till binär och decennium.Den förinställer via JAM-ingångar efter att ha fått en högaktivitetssignal och återställs till noll när Low Enable är engagerad.Denna anpassningsförmåga stöder applikationer som kräver exakta signalbehandlingskonfigurationer.Praktisk kunskap om sin verksamhet säkerställer att CD4029 kan smidigt hantera återställningar och lägesövergångar, vilket återspeglar en omfattande förståelse av kontrolldynamiken i digitala kretsar.

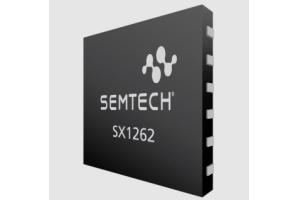

Den ultimata guiden till SX1262 -chipmodulen

på 2024/11/29

Omfattande jämförelse: LM324 vs LM358 Operationella förstärkare

på 2024/11/28

Populära inlägg

-

Komplexa instruktionsuppsättningsdatorer: Hur de ändrade datoranvändning?

på 8000/04/18 147764

-

USB-C-pinout och funktioner

på 2000/04/18 111989

-

Använda Xilinx Unified Simulation Primitives: En omfattande guide till FPGA -design och simulering

på 1600/04/18 111351

-

Strömförsörjningsspänningar i elektronik: Betydelsen av VCC, VDD, VEE, VSS och GND

på 0400/04/18 83751

-

RJ45 -anslutningsguide: Pinout, ledningar, kabeltyper och användningar

på 1970/01/1 79546

-

Den ultimata guiden för trådfärgkoder i moderna elektriska system

Hur våra elektriska system använder färger är inte bara för utseende.Varje trådfärg indikerar nu en specifik funktion, vilket gör det lättare att identifiera och hantera elektriska komponenter korr...på 1970/01/1 66949

-

Purge Valve Guide: Funktion, symtom, testning och ersättning för optimal motorprestanda

Purge -ventilen är en viktig del av bilens system som hjälper till att hålla luften ren genom att hantera bränsleångor innan de kan fly in i atmosfären.Detta hjälper inte bara miljön genom att mins...på 1970/01/1 63094

-

Kvalitet (Q) Faktor: Ekvationer och applikationer

Kvalitetsfaktorn, eller 'Q', är viktig när man kontrollerar hur väl induktorer och resonatorer arbetar i elektroniska system som använder radiofrekvenser (RF).'Q' mäter hur väl en krets minimerar e...på 1970/01/1 63028

-

Uppnå toppprestanda med den maximala kraftöverföringssatsen

Den maximala kraftöverföringssatsen förklarar hur energi från en källa, till exempel ett batteri eller generator, flyter till en ansluten belastning.Det visar det exakta tillståndet där lasten får ...på 1970/01/1 54092

-

A23 -batterispecifikationer och kompatibilitet

A23-batteriet är ett litet, cylinderformat batteri med högspänning.Även kallad 23A, 23AE eller MN21, den körs vid 12 volt och mycket högre än AA- eller AAA -batterier.Dess speciella design...på 1970/01/1 52172