EP1C4F400C8 FPGA: Funktioner, specifikationer, programmering och alternativ

Om du arbetar med programmerbar logik ger EP1C4F400C8 dig en praktisk balans mellan prestanda och kostnad.I den här artikeln kommer du att lära dig vad denna FPGA är, dess nyckelfunktioner som logikkapacitet, minne och I/O -alternativ och hur dess struktur stöder tillförlitlig design.Du kommer också att se dess specifikationer, applikationer i system, programmeringsprocess och hur den jämförs med liknande delar.Katalog

Vad är EP1C4F400C8?

De EP1C4F400C8 är medlem i Intels (tidigare Alteras) Cyclone FPGA-familj, designad som en kostnadseffektiv och pålitlig programmerbar logiklösning.Denna enhet bygger på en 0,13 um SRAM-process och erbjuder måttlig logikdensitet och flexibla I/O-alternativ inom ett kompakt FBGA-400-paket.Cyclone -familjen, som inkluderar enheter som EP1C3, EP1C6, EP1C12 och EP1C20, skapades för att balansera prestanda och prisvärd för skalbara konstruktioner, vilket möjliggör enkel migration mellan densitetsnivåer och paket.Känd för stabilitet och bred adoption, är det fortfarande ett betrodd val i äldre design.

Letar du efter EP1C4F400C8?Kontakta oss för att kontrollera nuvarande lager, ledtid och prissättning.

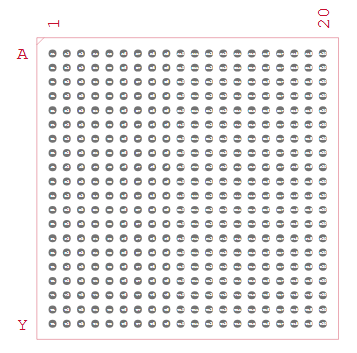

EP1C4F400C8 CAD -modeller

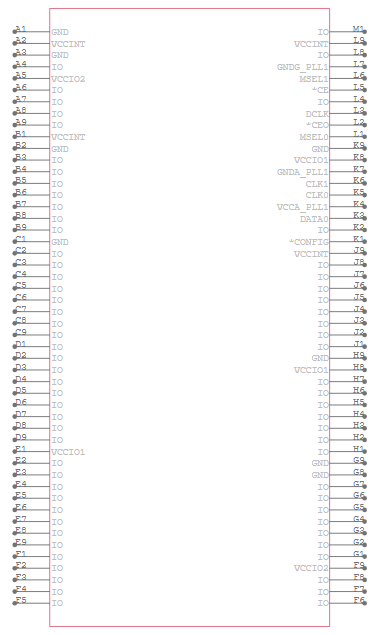

EP1C4F400C8 -symbol

EP1C4F400C8 fotavtryck

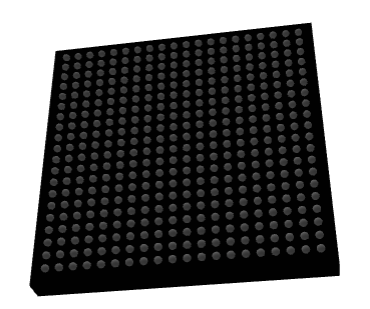

EP1C4F400C8 3D -modell

EP1C4F400C8 -funktioner

• Logikkapacitet

EP1C4F400C8 erbjuder cirka 4 000 logikelement, organiserade i 400 logiska arrayblock (LAB).Detta gör det lämpligt för mellanklasskonstruktioner som kräver måttlig logikdensitet samtidigt som kostnadseffektiviteten bibehålls.

• Inbäddat minne

Den integrerar cirka 76,5 kbits inbäddat minne.Denna interna RAM stöder databuffring, lagring och små minnesfunktioner, vilket minskar behovet av externa minneskomponenter i många konstruktioner.

• Hög I/O -räkning

Enheten tillhandahåller 301 användarkonfigurerbara I/O-stift i sitt 400-boll FBGA-paket.Detta höga stiftantal möjliggör rik anslutning för komplexa system som kräver flera perifera gränssnitt.

• Breda I/O -standarder stöder

Det stöder flera I/O-standarder inklusive LVTTL, LVCMOS, SSTL-2, SSTL-3 och differentiella LVD-skivor.Denna flexibilitet gör det möjligt för FPGA att gränssnitt direkt med en mängd moderna logikfamiljer och minnesenheter.

• Höghastighetsdifferentialsignalering

Med LVDS -stöd upp till 640 Mbps hanterar FPGA snabba dataöverföringskrav.Detta gör det praktiskt för applikationer som höghastighetskommunikationslänkar och snabba digitala gränssnitt.

• Klockhantering med PLLS

Chipet integrerar två faslåsta slingor (PLL) och åtta globala klocknät.Dessa funktioner tillåter exakt klockgenerering, multiplikation och jitterkontroll för tidskritiska applikationer.

• Lågspänningskärnoperation

Driften vid en nominell 1,5 V -kärnspänning, balanserar enheten prestanda med lägre strömförbrukning.Denna spänningsnivå optimerades för den 0,13 um CMOS-tekniken som användes i dess tillverkning.

• Flexibla I/O -spänningar

FPGA stöder I/O -spänningar på 1,5 V, 1,8 V, 2,5 V och 3,3 V över olika banker.Denna mångsidighet gör det möjligt att gränssnitt med både arv och moderna systemkomponenter.

• SRAM-baserad konfiguration

Liksom andra Cyclone FPGA: er är den SRAM-baserad och kräver rekonfiguration vid varje power-up.Detta ger flexibilitet för uppdateringar men kräver också en extern konfigurationsenhet eller styrenhet.

• Bitstream -kompressionsstöd

EP1C4F400C8 stöder komprimerad bitströmbelastning under konfigurationen.Detta minskar kraven på externa minnes och påskyndar konfigurationstider.

• PCI -efterlevnad

Det inkluderar inbyggt stöd för PCI-standarder (33/66 MHz, 32/64-bitars).Denna funktion gör det möjligt att integrera enheten direkt i system som kräver PCI -gränssnitt utan ytterligare överbryggande logik.

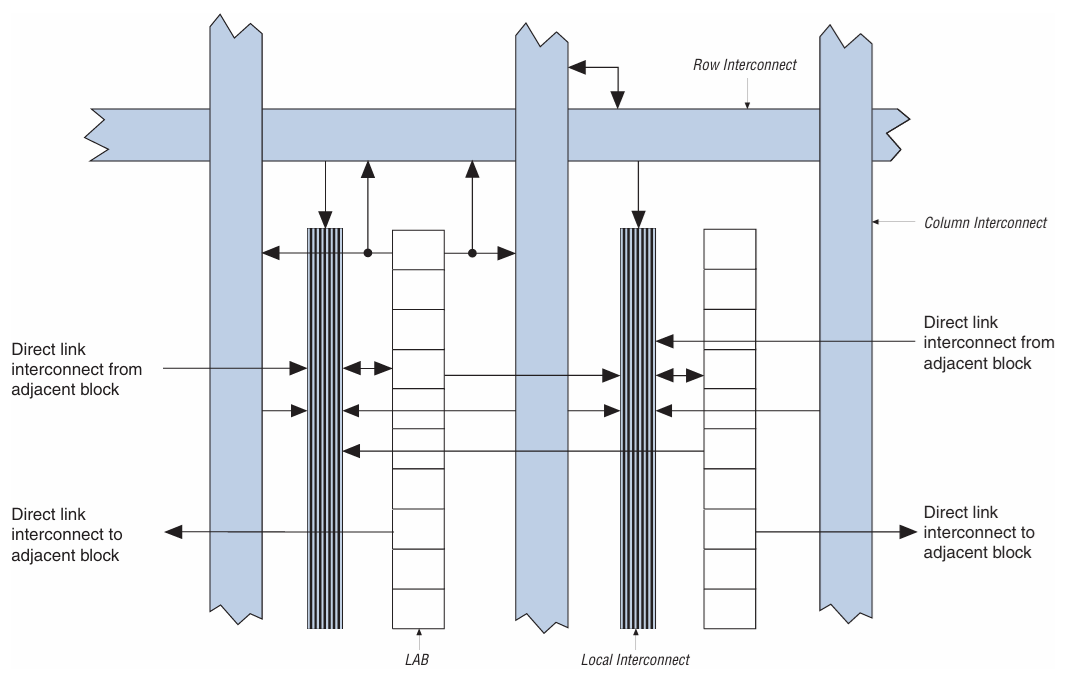

Cyklonlaboratorium

Diagrammet visar strukturen Logic Array Block (LAB) som används i Cyclone FPGA som EP1C4F400C8.Varje labb ansluter till ett nätverk av sammankopplingar: radförbindelser, kolumnförbindelser och lokala sammankopplingar, som rutt signaler mellan logikelement och andra block.Direct Link-sammankopplingar ger snabba vägar med låg latens till angränsande labb, vilket förbättrar tidsresultatet i signalvägar.Denna arkitektur är viktig eftersom den balanserar routing flexibilitet med effektivitet, vilket gör det möjligt för FPGA att hantera komplexa mönster samtidigt som hastigheten och området är optimerat.

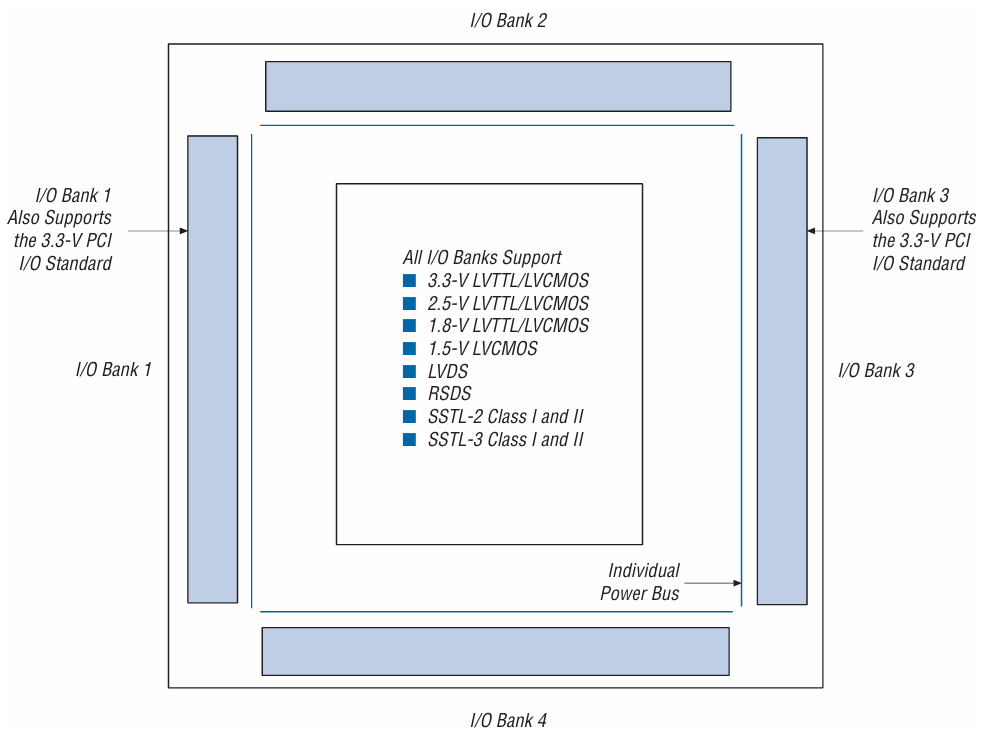

Cyklon I/O Banks -diagram

Diagrammet illustrerar I/O -bankstrukturen för Cyclone FPGAS såsom EP1C4F400C8.Enheten är uppdelad i fyra I/O -banker, var och en drivs av sin egen försörjningsbuss, vilket gör det möjligt att blanda olika spänningsstandarder inom en enda FPGA.Alla banker stöder ett brett utbud av I/O-standarder inklusive LVTTL, LVCMOS, LVD, RSD och SSTL, medan Banks 1 och 3 också stöder 3,3-V PCI för kompatibilitet med Legacy Systems.Denna flexibla I/O -arkitektur är viktig eftersom den möjliggör sömlös integration med olika externa enheter och gränssnitt, vilket gör FPGA anpassningsbar till olika applikationer.

EP1C4F400C8 -specifikationer

|

Typ |

Parameter |

|

Tillverkare |

Altera/intel |

|

Serie |

Cyclone® |

|

Förpackning |

Bricka |

|

Delstatus |

Föråldrad |

|

Antal laboratorier/clbs |

400 |

|

Antal logikelement/celler |

4000 |

|

Totala RAM -bitar |

78,336 |

|

Antal I/O |

301 |

|

Spänning - försörjning |

1.425V ~ 1.575V |

|

Monteringstyp |

Ytfäste |

|

Driftstemperatur |

0 ° C ~ 85 ° C (TJ) |

|

Förpackning / fodral |

400-bga |

|

Leverantörspaket |

400-FBGA (21 × 21) |

|

Basproduktnummer |

Ep1c4 |

EP1C4F400C8 -applikationer

1. Digital signalbehandling (DSP)

EP1C4F400C8 kan programmeras för att utföra uppgifter som filtrering, FFT och signalmodulering.Dess kombination av logikelement och inbäddat minne gör det lämpligt för höghastighetsbehandling.Detta gör att den kan ersätta traditionella DSP -chips med en flexibel FPGA -lösning som kan omprogrammeras för olika algoritmer.

2. Inbäddade och styrsystem

I industriella och inbäddade system används denna FPGA ofta för att implementera anpassade styrenheter, sequencers och statliga maskiner.Dess omkonfigurerbara logik gör det möjligt att skräddarsy hårdvarubeteende exakt efter systembehov.Genom att integrera kontrolllogik i FPGA reduceras antalet externa komponenter, vilket förbättrar tillförlitligheten och sänker kostnaden.

3. Kommunikations- och gränssnittsbryggning

Enheten stöder flera I/O -standarder och kan fungera som en bro mellan olika kommunikationsprotokoll.Det används ofta för att ansluta PCI, LVD -skivor, SDRAM och andra gränssnitt sömlöst inom ett system.Detta gör det mycket användbart i nätverksutrustning, inbäddade styrenheter och arv-till-moderna gränssnittskonverteringar.

4. Datainsamling och bearbetning

Med hög I/O-tillgänglighet och flexibelt minne är EP1C4F400C8 väl lämpad för datainsamlingssystem.Det kan direkt gränssnittet med ADC: er och sensorer, bearbeta data i tid och förbereda dem för lagring eller överföring.Sådana applikationer är vanliga i medicinska instrument, testutrustning och vetenskapliga mätanordningar.

EP1C4F400C8 Liknande delar

|

Specifikation |

EP1C4F400C8 |

EP1C4F400C8N |

EP1C4F400C8NAA |

EP1C4F400C6N |

EP1C4F324C8N |

EP1C4T144C8N |

|

Tillverkare |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

|

FPGA -familj |

Cyklon (EP1C4) |

Cyklon (EP1C4) |

Cyklon (EP1C4) |

Cyklon (EP1C4) |

Cyklon (EP1C4) |

Cyklon (EP1C4) |

|

Logikelement (LES) |

4 000 |

4 000 |

4 000 |

4 000 |

4 000 |

4 000 |

|

Inbäddat minne (bitar) |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

|

I/O -stift |

301 |

301 |

301 |

301 |

249 |

97 |

|

Förpackning / fodral |

400-fbga |

400-fbga |

400-fbga |

400-fbga |

324-fbga |

144-TQFP |

|

Hastighetsgrad |

C8 |

C8 |

C8 |

C6 (snabbare) |

C8 |

C8 |

|

Kärnspänning |

1,5 v |

1,5 v |

1,5 v |

1,5 v |

1,5 v |

1,5 v |

|

Operativ temp.Räckvidd |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C

|

EP1C4F400C8 -programmeringssteg

Innan du kan använda EP1C4F400C8 FPGA måste du ladda din design i enheten.Programmering innebär att konfigurera FPGA med en bitströmfil så att den vet hur du ska bete sig som din avsedda krets.

1. Välj konfigurationsschema och set msel Pins

Du börjar med att välja det konfigurationsschema som bäst passar din installation, till exempel aktiv serie, passiv serie eller JTAG.Detta görs genom att ställa in MSEL-stiften till specifika logiknivåer före power-up.Varje läge använder olika stift och protokoll, så du måste bekräfta kompatibilitet med dina designverktyg och konfigurationsminne.Att göra rätt val här säkerställer en smidig konfigurationsprocess.

2. Applicera ström och initialisera enheten

Därefter kör du upp FPGA: s kärn- och I/O -skenor inom de angivna spänningsområdena.Under start, håll NConfig -stiftet låg för att hålla enheten i återställning tills matningsspänningarna är stabila.När du är stabil släpper du återställning och enhetssignalerna beredskap genom att köra nstatus -stiftet.Detta garanterar att FPGA är korrekt initialiserad innan konfigurationen börjar.

3. Överföra konfigurationen Bitstream

I detta skede skickar du konfigurationsdatafilen (Bitstream) till FPGA med ditt valda schema.I aktivt serie- eller passivt serieläge kommer bitströmmen från en extern minnesanordning, medan JTAG tillåter direkt programmering via kabel.Enheten läser kontinuerligt i konfigurationsdata tills den är klar.Din designprogramvara genererar denna bitström för att matcha dina logikkrav.

4. Bekräfta framgångsrik konfiguration (conf_done)

När FPGA slutar laddas, hävdar den Conf_Done -stiftet för att visa att konfigurationsdata framgångsrikt mottogs.Samtidigt utför enheten intern initialisering såsom rensningsregister och aktivering av I/O.Om Conf_Done inte går högt, betyder det vanligtvis att konfigurationsdata eller installation har ett fel.Att titta på denna stift är det enklaste sättet att verifiera att processen är klar.

5. Utför valfritt in-system-rekonfiguration

Slutligen har du möjlighet att uppdatera eller omprogrammera FPGA utan att ta bort den från styrelsen.Med JTAG eller en inbäddad styrenhet kan du ladda en ny bitström direkt, vilket är användbart för firmware -uppdateringar.Denna flexibilitet gör att du kan ändra, felsöka eller uppgradera ditt system även efter distributionen.Det säkerställer att din FPGA-baserade design kan anpassa sig över tid till förändrade krav.

EP1C4F400C8 Fördelar och nackdelar

Fördelar

• Kostnadseffektivt val för mellanklassdesign

• Hög I/O -räkning jämfört med liknande densitetsenheter

• Flexibel spänning och I/O -standardstöd

• Stöds av mogna verktyg och dokumentation

• Lägre kraftanvändning än äldre FPGA -generationer

Nackdelar

• föråldrad med begränsad långsiktig tillgänglighet

• Lägre logik och minneskapacitet kontra moderna FPGA: er

• Långsammare driftshastighet och I/O -prestanda

• Kräver externt minne för konfiguration vid power-up

• saknar avancerade funktioner som DSP-block och höghastighetsändtagare

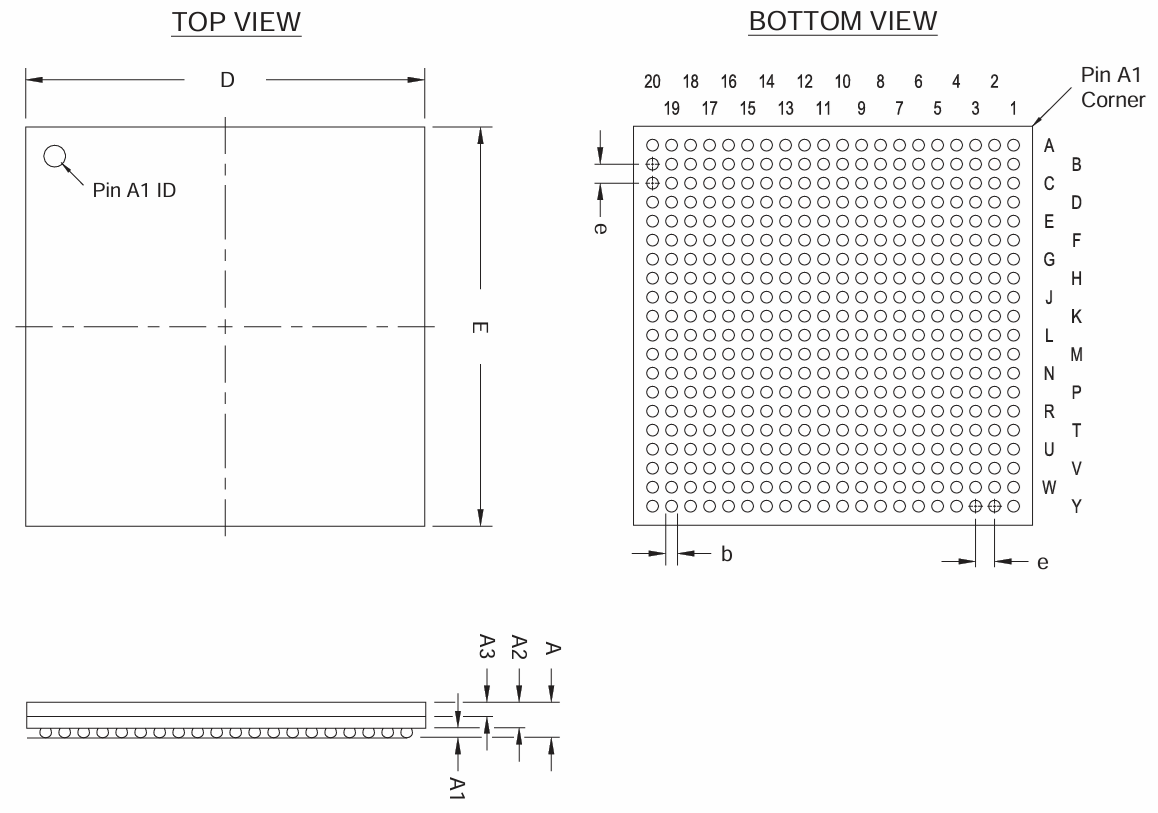

EP1C4F400C8 förpackningsdimensioner

|

Typ |

Parameter |

|

Pakettyp |

FBGA (Fine-Pitch Ball Grid Array) |

|

Bollräkning |

400 |

|

Bollhöjd (e) |

1,0 mm (typisk för cyklon EP1C4F400) |

|

Kuldiameter (b) |

0,45 mm (nominell) |

|

Paketstorlek (D × E) |

21 mm × 21 mm |

|

Pakethöjd (a) |

2,40 mm (max) |

|

Substrattjocklek (A2) |

~ 0,40 mm |

|

Mögelmössa tjocklek (A3) |

~ 1,90 mm |

|

Bollhöjd (A1) |

0,25 mm (nominell) |

|

Stift A1 hörn |

Markerad för orientering |

|

Matrislayout |

20 × 20 rutnät (med hörnbollar saknas) |

|

Montering |

Ytmontering (SMD) |

EP1C4F400C8 -tillverkare

EP1C4F400C8 tillverkades ursprungligen av Anläggningsföretag, en pionjär inom programmerbara logikenheter och FPGA -teknik.2015 förvärvades altera av Intel Corporationoch produktlinjen blev en del av Intels programmerbara Solutions Group (PSG).Idag stöder Intel dessa Legacy Altera -enheter medan de fokuserar utvecklingen på nyare FPGA -familjer, säkerställer kontinuitet för befintliga användare och främjar innovation inom programmerbar logik.

Slutsats

EP1C4F400C8 sticker ut som en kostnadseffektiv och mångsidig FPGA som erbjuder solid prestanda för mellanklassdesign.Med sina 4 000 logikelement, inbäddat minne, omfattande I/O -stöd och kompatibilitet med flera spännings- och gränssnittsstandarder ger det flexibilitet i olika applikationer.Dess arkitektur, programmeringsprocess och bred användbarhet i DSP, inbäddade system och datainsamling gör det till ett praktiskt val trots dess arvstatus.Även om det saknar avancerade funktioner som finns i nyare enheter och ansikten begränsad långsiktig tillgänglighet, är det fortfarande ett pålitligt alternativ som söker beprövade lösningar i skalbara FPGA-mönster.

Datablad pdf

EP1C4F400C8 Datablad:

Om oss

ALLELCO LIMITED

Läs mer

Snabb förfrågan

Skicka en förfrågan, vi svarar omedelbart.

Vanliga frågor [FAQ]

1. Vilka verktyg krävs för att programmera EP1C4F400C8?

Du behöver Intels Quartus-programvara (tidigare Altera Quartus II) tillsammans med en stödd programmeringskabel som USB-Blaster.Dessa verktyg gör att du kan skapa bitströmmen och ladda den i FPGA.

2. Kan EP1C4F400C8 hantera PCI -applikationer direkt?

Ja, det har inbyggd efterlevnad för PCI-standarder (33/66 MHz, 32/64-bitars), vilket gör det lämpligt för PCI-baserad systemintegration utan att kräva extra överbryggande logik.

3. Vad händer om EP1C4F400C8 misslyckas under konfigurationen?

Om konfigurationen misslyckas, kommer inte Conf_Done -stiftet att hävda högt.Detta pekar vanligtvis på ett fel i bitströmsfilen, spänningssekvensen eller stiftinställningen och bör kontrolleras i ditt designflöde.

4. Kan EP1C4F400C8 -gränssnittet direkt med DDR -minne?

Det stöder flera I/O -standarder men har inte inbyggda DDR -gränssnitt som moderna FPGA.Ytterligare designöverväganden eller överbryggningskomponenter kan behövas.

5. Hur jämför EP1C4F400C8 med nyare FPGA?

Jämfört med moderna enheter har EP1C4F400C8 lägre hastighet, mindre logikdensitet och färre avancerade funktioner.Det är emellertid ett kostnadseffektivt val för stabila mellankonstruktioner där banbrytande prestanda inte krävs.

EPM3256AFC256-7 CPLD Översikt: Funktioner, pinout, programmering och applikationer

på 2025/10/3

ADG432BR Analog switch IC: Specifikationer, pinout, alternativ och datablad

på 2025/10/2

Populära inlägg

-

Komplexa instruktionsuppsättningsdatorer: Hur de ändrade datoranvändning?

på 8000/04/18 147772

-

USB-C-pinout och funktioner

på 2000/04/18 112009

-

Använda Xilinx Unified Simulation Primitives: En omfattande guide till FPGA -design och simulering

på 1600/04/18 111351

-

Strömförsörjningsspänningar i elektronik: Betydelsen av VCC, VDD, VEE, VSS och GND

på 0400/04/18 83768

-

RJ45 -anslutningsguide: Pinout, ledningar, kabeltyper och användningar

på 1970/01/1 79565

-

Den ultimata guiden för trådfärgkoder i moderna elektriska system

Hur våra elektriska system använder färger är inte bara för utseende.Varje trådfärg indikerar nu en specifik funktion, vilket gör det lättare att identifiera och hantera elektriska komponenter korr...på 1970/01/1 66960

-

Purge Valve Guide: Funktion, symtom, testning och ersättning för optimal motorprestanda

Purge -ventilen är en viktig del av bilens system som hjälper till att hålla luften ren genom att hantera bränsleångor innan de kan fly in i atmosfären.Detta hjälper inte bara miljön genom att mins...på 1970/01/1 63100

-

Kvalitet (Q) Faktor: Ekvationer och applikationer

Kvalitetsfaktorn, eller 'Q', är viktig när man kontrollerar hur väl induktorer och resonatorer arbetar i elektroniska system som använder radiofrekvenser (RF).'Q' mäter hur väl en krets minimerar e...på 1970/01/1 63040

-

Uppnå toppprestanda med den maximala kraftöverföringssatsen

Den maximala kraftöverföringssatsen förklarar hur energi från en källa, till exempel ett batteri eller generator, flyter till en ansluten belastning.Det visar det exakta tillståndet där lasten får ...på 1970/01/1 54097

-

A23 -batterispecifikationer och kompatibilitet

A23-batteriet är ett litet, cylinderformat batteri med högspänning.Även kallad 23A, 23AE eller MN21, den körs vid 12 volt och mycket högre än AA- eller AAA -batterier.Dess speciella design...på 1970/01/1 52184