EPF10K30ATC144-1 FPGA: Funktioner, applikationer, programmering och alternativ förklarade

Den här guiden handlar om EPF10K30ATC144-1, en typ av FPGA-chip.Det förklarar vad chipet är, hur det fungerar och var det kan användas.Du kommer att lära dig om dess huvudfunktioner som inbyggt minne, flexibla logikblock och stöd för både 3.3V- och 5V-system.Det visar också hur man använder chipet i projekt som ljud/videosystem, industrimaskiner och medicintekniska produkter.Det innehåller steg-för-steg-installationsinstruktioner, jämförelse av del och designverktyg som hjälper dig att förstå och arbeta med denna FPGA enkelt.Katalog

Vad är EPF10K30ATC144-1?

De EPF10K30ATC144-1 är medlem i Flex10k FPGA -familjen, utformad för att leverera inbäddad programmerbar logik med måttlig komplexitet och hög flexibilitet.Denna enhet byggd med 0,3-mikron CMOS SRAM-teknik och stöder cirka 30 000 användbara grindar och inkluderar 1 728 logikelement organiserade i logikuppsättningsblock (LAB).Den fungerar på 3,3V.Hastighetsgraden –1 -versionen erbjuder relativt snabb drift, med kärnfrekvenser upp till cirka 166 MHz.Enheten integrerar inbäddade arrayblock (EABS) för minne på chip, som förbättrar datahantering och kontrolloperationer i inbäddade mönster.Det används allmänt i industriell kontroll, kommunikation och arv inbäddade system och ger en programmerbar lösning med starkt I/O-stöd och tillräcklig logikkapacitet för ett brett spektrum av mitten av nivåer.Familjen Flex10K var en av de första FPGA-linjerna som kombinerade SRAM-baserade logik och inbäddade RAM-block, vilket gav skalbara alternativ från 10K till över 200K systemgrindar.Med TTL-kompatibla I/OS och inbäddade minnesblock erbjuder Flex10K-enheter en balanserad kombination av logisk densitet, integration och prestanda för äldre designekosystem.

Letar du efter EPF10K30ATC144-1?Kontakta oss för att kontrollera nuvarande lager, ledtid och prissättning.

EPF10K30ATC144-1 CAD-modeller

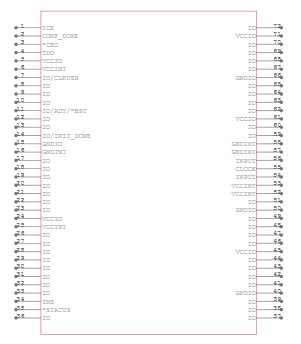

EPF10K30ATC144-1 Symbol

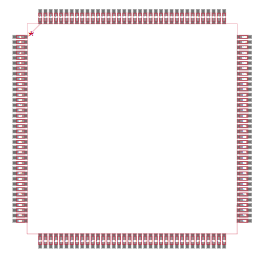

EPF10K30ATC144-1 Fotavtryck

EPF10K30ATC144-1 3D-modell

EPF10K30ATC144-1 Funktioner

• Högdensitetsarkitektur

EPF10K30ATC144-1 är byggd med Alteras Flex 10K-arkitektur och erbjuder upp till 69 000 systemgrindar och 1 728 logikelement (LES).Dessa logikelement fungerar som byggstenar för att implementera logikfunktioner och digitala mönster.Denna höga logikdensitet stöder måttligt komplexa digitala system såsom tillståndsmaskiner, små processorer och kontrolllogik på ett enda chip.

• Inbäddade arrayblock (EAB)

Den här enheten innehåller flera inbäddade arrayblock, som tillhandahåller cirka 12,3 kilobits RAM.Varje EAB erbjuder 2 048 bitar som kan konfigureras som RAM eller ROM, vilket stöder bitbredd upp till 256. Dessa block tillåter snabb och flexibel minnesintegration i FPGA utan att konsumera logikelement, vilket gör det idealiskt för buffring, uppslagning av tabeller och små datalagring inom chip.

• Rekonfigurerbar SRAM-baserad logik

EPF10K30ATC144-1 använder SRAM-teknik för sin programmerbara logik.Detta innebär att det kan omprogrammeras ett obegränsat antal gånger, vilket är värdefullt under prototyper och systemuppgraderingar.Du kan testa, modifiera och verifiera deras kretsfunktioner flera gånger innan den slutliga distributionen.

• 3.3V kärndrift med 5V -tolerant I/O

Denna FPGA fungerar med en 3,3V-tillförsel för intern logik men stöder 5V-toleranta I/O-stift.Denna dubbelspänningskompatibilitet säkerställer att enheten säkert kan gränssnitt med Legacy 5V-komponenter samtidigt som den moderna lågspänningseffektiviteten bibehålls för kärnfunktioner.Det förenklar designen med blandad spänningar utan att behöva nivåskiftare.

• Höghastighetsklockor

Enheten stöder driftsfrekvenser upp till 166,67 MHz, vilket möjliggör snabb databehandling och signalhantering i tidskritiska applikationer.Denna höga maximala frekvens gör EPF10K30ATC144-1 lämplig för höghastighetsstyrningssystem, kommunikation och inbäddade datoruppgifter.

• Låg effekt standby -läge

FPGA har låg statisk kraftförbrukning, med standbyström vanligtvis mindre än 0,5 mA.Detta gör att enheten kan användas i energikänsliga applikationer där tomgångseffekt måste minimeras, såsom bärbara instrument eller system med kraftbesparande lägen.

• Kommersiellt temperaturområde

Det är betygsatt för ett 0 ° C till +70 ° C temperaturintervall, som passar standardmiljöer.Detta säkerställer tillförlitlig drift under typiska inomhusförhållanden utan att kräva temperaturspecifikationer för industriell kvalitet.

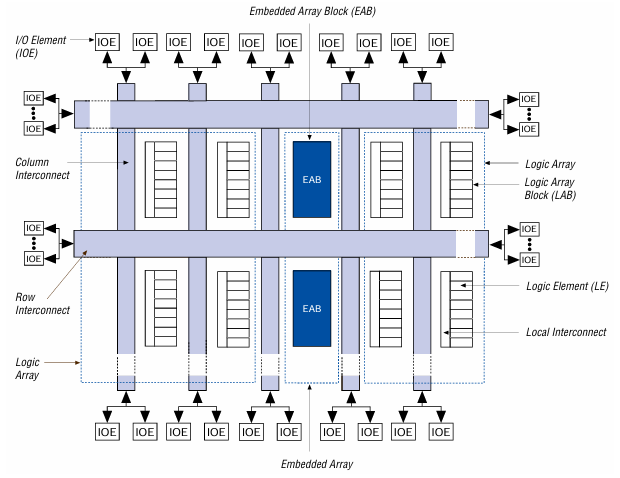

Flex 10k enhetsblockdiagram

Diagrammet representerar den interna arkitekturen för en FLEX 10K FPGA-enhet, särskilt EPF10K30ATC144-1.Kärnan i enheten är den inbäddade arrayen, som består av två primära typer av komponenter: logikuppsättningsblock (labb) och inbäddade arrayblock (EABS).Labs består av flera logikelement (LES) som hanterar allmänna logikfunktioner.Varje LE är ansluten genom en lokal sammankoppling, vilket möjliggör flexibel logikimplementering inom labbet.

Omger laboratorierna är de inbäddade arrayblocken (EABS), som visas i mörkblå.Dessa är minnesblock med hög täthet som används för funktioner som RAM eller ROM, vilket möjliggör inbäddad databehandling eller buffring direkt i FPGA-tyget.Kolumnen och raden sammankopplar möjliggör kommunikation mellan labb, EAB: er och I/O -element (IOE) placerade runt chipets omkrets.Dessa sammankopplingar stöder komplexa routingvägar och är viktiga för dataflödet över olika logikavsnitt.

Varje IOE ansluter den interna logiken till externa stift, vilket gör att enheten kan gränssnitt med andra systemkomponenter.Strukturen är modulär och symmetrisk och erbjuder effektiv layout för routing och skalbarhet.I EPF10K30ATC144-1 möjliggör detta arrangemang en balanserad blandning av programmerbar logik och inbäddat minne, idealiskt för digitala system för medelstora komplexitet som behöver snabb datahantering och flexibel logikkonfiguration.

EPF10K30ATC144-1-specifikationer

|

Typ |

Parameter |

|

Tillverkare |

Altera/intel |

|

Serie |

Flex-10ka® |

|

Förpackning |

Bulk |

|

Delstatus |

Aktiv |

|

Antal laboratorier/clbs |

216 |

|

Antal I/O |

102 |

|

Spänning - försörjning |

3V ~ 3,6V |

|

Monteringstyp |

Ytfäste |

|

Driftstemperatur |

0 ° C ~ 70 ° C (TA) |

|

Förpackning / fodral |

144-LQFP |

|

Leverantörspaket |

144-TQFP (20x20) |

|

Basproduktnummer |

EPF10K30 |

EPF10K30ATC144-1 Applikationer

Digital Audio / Video -bearbetning

EPF10K30ATC144-1 är väl lämpad för ljud- och videobearbetningsuppgifter på grund av dess inbäddade arrayblock (EABS) som ger RAM-chip.Denna funktion möjliggör buffring, tillfällig lagring och datamanipulation direkt inom FPGA.Många använder ofta denna FPGA för att hantera ljudströmavkodning, pixelmanipulation eller tidpunkt för digital videogränssnitt.Dess måttliga logikkapacitet och I/O -flexibilitet möjliggör integration med codecs, tidskontroller och synkroniseringslogik i multimediasystem.

Industrikontrollsystem

I industriell automatisering kan EPF10K30ATC144-1 fungera som en central kontroller eller intelligent I/O-gränssnitt.Dess programmerbara logik stöder implementering av tillståndsmaskiner, sensorgränssnitt, datainsamling och seriekommunikationsprotokoll som SPI eller RS-485.Tillgängligheten till RAM-chip och stort I/O-räkning gör det lämpligt för att hantera flera styrsignaler i programmerbara logikstyrenheter (PLC), motoriska enheter eller robotundersystem.

Medicinsk utrustning

Medicinsk utrustning kräver exakt, rekonfigurerbar logik för att hantera specialiserade dataflöden.Denna FPGA kan användas för signalkonditionering, filtrering och bearbetning av analoga sensoringångar i applikationer som EKG, ultraljud eller bildsystem.Dess förutsägbara latens och flexibla programmering gör det idealiskt för att integrera proprietära algoritmer eller förbehandlingssteg för data före ytterligare mikrokontroller eller DSP -hantering.

Bil- och rymdelektronik

I fordonsdashboards, flyg- och rymdkontrollenheter användes vanligtvis EPF10K30ATC144-1 för gränssnittssensorer, hantering av diagnostik eller implementering av kommunikationsprotokoll.Dess omprogrammerbara natur fick justera logik efter distribution eller under systemvalidering.Delens I/O -flexibilitet gjorde att den kan överbrygga mellan äldre bussar och moderna kommunikationssystem samtidigt som stabilitet i robusta miljöer.

Kommunikations- och nätverkssystem

Tack vare dess förmåga att implementera anpassade seriella protokoll och datafiltreringslogik hittades EPF10K30ATC144-1 Användning i äldre telekomsystem och nätverksbackplan.Dess inbäddade RAM stöder buffring och pakethuvudanalys, medan logikblock kan implementera växlingsregler eller paritetskontroller.Det fungerade som ett limlogikelement och hjälpte till att integrera processorer, switchar och signalvägar i kommunikationsinfrastruktur.

EPF10K30ATC144-1 Liknande delar

EPF10K30AQI208-3 är ett starkt alternativ till EPF10K30ATC144-1, och erbjuder samma logikelementräkning (1 728 LES) och inbäddat minne (~ 12,3 kbit) men med ett större 208-stifts QFP-paket.Det ökar antalet tillgängliga I/O -stift till 147, vilket gör det idealiskt för applikationer som kräver mer externa anslutningar.Med en industrikvalitet –3 hastighetsgradering presterar den pålitligt över ett bredare temperaturintervall på –40 ° C till +85 ° C.Detta gör det lämpligt för robusta miljöer i telekom, kontrollsystem och robusta industriella installationer.Dess utvidgade I/O och driftsintervall gör det till en praktisk uppgradering för mönster som växer ut med 144-stifts TQFP-konfiguration.

EPF10K30AQI240-3 är en annan kompatibel FPGA i Flex 10K-familjen, vilket erbjuder högre I/O-densitet med ett 240-stifts QFP-paket och 189 I/O-stift.Liksom ATC144-1 upprätthåller den 1 728 logikelement och 12,3 kbit inbäddad RAM.Dess –3 hastighetsgrad säkerställer konsekvent prestanda vid industriella temperaturer, vilket gör det till ett pålitligt val för system med breda miljöfluktuationer.Det är väl lämpat för applikationer med hög pin-count som komplexa kontrollpaneler, inbäddade videosystem och äldre datorgränssnitt.

EPF10K30AQC240-3 tillhandahåller också 189 I/O-stift i en 240-polig QFP-layout och upprätthåller kärnarkitekturen på 1 728 LES och ~ 12 kbit av-chip-RAM.Även om det nu är listat som föråldrat, förblir det en livskraftig ersättning i system där det mekaniska fotavtrycket och signalpinout för 240-poliga QFP behövs.Det är funktionellt identiskt med AQI240-3 men används vanligtvis i kommersiella temperaturapplikationer.Denna del är värdefull för äldre underhåll av hårdvara, särskilt när drop-in mekanisk kompatibilitet med 240-stifts layout behövs, och att köpa nya mönster är inte genomförbart.

EPF10K30ATC144-1 Programmeringssteg

1. Skapa och sammanställa designen

Börja med att utforma din digitala logik med en HDL som VHDL eller Verilog.Använd programvaruverktyg som Altera Quartus II eller Max+Plus II för att bygga projektet.När din design är klar, kompilera den för att generera programmeringsfiler.Du får en .SOF-fil för SRAM-baserad JTAG-konfiguration och en .poF-fil om du vill programmera en seriell EEPROM för power-up-lastning.

2. Välj konfigurationsmetoden

Det finns två huvudsakliga sätt att konfigurera EPF10K30ATC144-1.För tillfällig programmering under testning eller utveckling, använd JTAG -konfiguration med .SOF -filen.För permanent eller automatisk konfiguration vid systemstart, använd den passiva seriella metoden genom att ladda .poF -filen i en extern EEPROM (som EPC2).

3. Anslut och programmera enheten

Om du använder JTAG, anslut en programmeringskabel (t.ex. USB-Blaster) till JTAG-rubriken.Öppna Quartus -programmerare, ladda .SOF -filen och programmera enheten direkt.För passiv serie, anslut EEPROM till FPGA och använd kvartus för att programmera .poF -filen till EEPROM.Vid power-up skickar EEPROM bitströmmen till FPGA.

4. Omprogrammering vid behov

EPF10K30ATC144-1 kan omprogrammeras när som helst via JTAG.Du kan också uppdatera EEPROM -innehållet för att ändra startkonfigurationen.Detta är användbart för fältuppdateringar eller designförbättringar.

5. Verifiera programmeringssucces

Efter programmering, kontrollera FPGA: s statusstift (nstatus och conf_done) för att bekräfta framgångsrik konfiguration.Du kan också köra funktionella tester eller använda felsökningsverktyg som SignalTap för att säkerställa att logiken fungerar som avsedd.

EPF10K30ATC144-1 Fördelar

• Hög integration med inbäddad RAM

EPF10K30ATC144-1 integrerar cirka 30 000 systemgrindar och 1 728 logikelement, tillsammans med cirka 12 kbits inbäddat RAM.Dessa inbäddade arrayblock (EABS) möjliggör snabbare och mer förutsägbara minnesoperationer jämfört med distribuerad RAM.Detta hjälper till att förenkla logikdesignen, särskilt i applikationer som kräver buffring, uppslagstabeller eller liten datalagring, vilket förbättrar både prestanda och resursanvändning.

• Blandningskompatibilitet

En av de starka fördelarna med denna enhet är dess förmåga att arbeta med 3,3V leverans samtidigt som 5V-tolerant I/OS stöder.Denna MULIVOLT ™ I/O -funktion gör FPGA flexibel för integration i system som använder både Legacy 5V -logik och moderna 3.3V -komponenter.Det är användbart i industriella eller kommunikationssystem där spänningsnivåerna varierar mellan delsystem.

• Enkel rekonfiguration

Eftersom den använder SRAM-teknik kan EPF10K30ATC144-1 enkelt omprogrammeras med antingen JTAG eller passiva seriemetoder.Du kan uppdatera logikfunktioner i fältet eller under utvecklingen utan att ersätta chipet.Detta minskar kostnaderna och möjliggör framtida uppgraderingar eller bugfixar efter distributionen.

• Inbyggd jtag och snabb utveckling

Enheten inkluderar inbyggt JTAG-stöd, möjliggör testning av gränsskanning och programmering i systemet.Detta är värdefullt för tillverkningstester och felsökning.Jämfört med traditionell ASIC-utveckling minskar också denna FPGA designtid för design, vilket gör den idealisk för snabb prototypning och små till mediumproduktionskörningar.

• Effektiv routing och prestationsarkitektur

Flex 10K -arkitekturen, som används i den här enheten, inkluderar FastTrack® -routing, bärkedjor för aritmetisk logik och klockträd som säkerställer förutsägbar timing och effektiv prestanda.Med sin –1-hastighetsgrad kan chipet fungera upp till cirka 166 MHz, vilket är lämpligt för många medelprestanda som signalkontroll, datahantering och protokollgränssnitt.

EPF10K30ATC144-1 Förpackningsdimensioner

• Pakettyp: TQFP -144 (Thin Quad Flat Package, 144 Pins)

• Montering: Ytmontering

• Kroppsstorlek: 20mm × 20 mm (inklusive leads)

• Stifthöjd: 0,80 mm (avstånd mellan stiftcentra)

• Kroppslängd (exklusive leads): 12,00 mm (nominell)

• Kroppsbredd (exklusive leads): 12,00 mm (nominell)

• Övergripande tjocklek: Upp till 1,20 mm

• Kroppstjocklek: Ungefär 0,95 mm

• Blylängd: 0,45 mm till 0,75 mm

• Ledningsbredd: 0,30 mm till 0,45 mm

• Sittplanhöjd (A1): 0,05 mm till 0,15 mm

EPF10K30ATC144-1 Tillverkare

EPF10K30ATC144-1 tillverkas av Alta , en pionjär inom programmerbara logikenheter och den ursprungliga utvecklaren av Flex 10K FPGA -serien.Grundades 1983 och blev ledande inom fältprogrammerbar Gate Array (FPGA) innovation och introducerade några av de tidigaste och mest använda programmerbara logiklösningarna i branschen.2015 förvärvades altera av Intel Företag, som fortsatte att stödja och integrera Alteras FPGA -produktlinjer under sin programmerbara Solutions Group (PSG).Även om Altera lanserades 2024 som ett separat Intel-dotterbolag, förblir EPF10K30ATC144-1 en Legacy FPGA som återspeglar Alteras ursprungliga teknik och tillverkningskompetens.

Slutsats

EPF10K30ATC144-1 är ett användbart och flexibelt FPGA-chip med bra minne, starka logikfunktioner och förmågan att arbeta med både nya och gamla system.Du kan omprogrammera det när som helst, vilket gör det bra för testning och uppdateringar.Det är lätt att ansluta och fungerar bra i många typer av elektronik, från fabriksmaskiner till nätverksverktyg.Även om det är en äldre del, hjälper det fortfarande i många projekt där pålitliga och omprogrammerbara chips behövs.

Datablad pdf

EPF10K30ATC144-1 Datablad:

Om oss

ALLELCO LIMITED

Läs mer

Snabb förfrågan

Skicka en förfrågan, vi svarar omedelbart.

Vanliga frågor [FAQ]

1. Kan jag använda EPF10K30ATC144-1 i moderna 3.3V-system?

Ja, EPF10K30ATC144-1 fungerar vid 3,3V och stöder också 5V-tolerant I/O, vilket gör det kompatibelt med både nya och äldre blandade spänningssystem.

2. Vilken programvara behöver jag för att programmera EPF10K30ATC144-1?

Du kan använda Alteras äldre designverktyg som Quartus II eller Max+Plus II för att skapa och programmera dina designfiler (.SOF och .POF).

3. Är EPF10K30ATC144-1 ett bra val för prototyper?

Ja, denna FPGA är idealisk för prototyper på grund av dess SRAM-baserade logik, vilket möjliggör obegränsad omprogrammering och snabb designförändringar.

4. Stöder EPF10K30ATC144-1 JTAG-programmering?

Ja, det stöder full JTAG-programmering och gränsskanning, vilket möjliggör konfiguration och testning i systemet under utvecklingen eller efter utplacering.

5. Vad är den maximala frekvensen EPF10K30ATC144-1 kan köras på?

Den stöder klockhastigheter upp till cirka 166 MHz, vilket gör det lämpligt för snabb signalbehandling och tidskritiska uppgifter.

Vad är en LDR och hur det fungerar inom elektronik

på 2025/06/17

ADG526AKRZ Analog multiplexer: Funktioner, pinout, applikationer och installationsguide

på 2025/06/17

Populära inlägg

-

Komplexa instruktionsuppsättningsdatorer: Hur de ändrade datoranvändning?

på 8000/04/18 147766

-

USB-C-pinout och funktioner

på 2000/04/18 111994

-

Använda Xilinx Unified Simulation Primitives: En omfattande guide till FPGA -design och simulering

på 1600/04/18 111351

-

Strömförsörjningsspänningar i elektronik: Betydelsen av VCC, VDD, VEE, VSS och GND

på 0400/04/18 83758

-

RJ45 -anslutningsguide: Pinout, ledningar, kabeltyper och användningar

på 1970/01/1 79552

-

Den ultimata guiden för trådfärgkoder i moderna elektriska system

Hur våra elektriska system använder färger är inte bara för utseende.Varje trådfärg indikerar nu en specifik funktion, vilket gör det lättare att identifiera och hantera elektriska komponenter korr...på 1970/01/1 66952

-

Purge Valve Guide: Funktion, symtom, testning och ersättning för optimal motorprestanda

Purge -ventilen är en viktig del av bilens system som hjälper till att hålla luften ren genom att hantera bränsleångor innan de kan fly in i atmosfären.Detta hjälper inte bara miljön genom att mins...på 1970/01/1 63096

-

Kvalitet (Q) Faktor: Ekvationer och applikationer

Kvalitetsfaktorn, eller 'Q', är viktig när man kontrollerar hur väl induktorer och resonatorer arbetar i elektroniska system som använder radiofrekvenser (RF).'Q' mäter hur väl en krets minimerar e...på 1970/01/1 63028

-

Uppnå toppprestanda med den maximala kraftöverföringssatsen

Den maximala kraftöverföringssatsen förklarar hur energi från en källa, till exempel ett batteri eller generator, flyter till en ansluten belastning.Det visar det exakta tillståndet där lasten får ...på 1970/01/1 54094

-

A23 -batterispecifikationer och kompatibilitet

A23-batteriet är ett litet, cylinderformat batteri med högspänning.Även kallad 23A, 23AE eller MN21, den körs vid 12 volt och mycket högre än AA- eller AAA -batterier.Dess speciella design...på 1970/01/1 52176