EPF8820ARC208-4 FPGA Guide: Funktioner, arkitektur, applikationer och programmering

Den här artikeln handlar om EPF8820ARC208-4, ett speciellt chip som används inom elektronik.Det förklarar vad chipet gör, hur det fungerar och var det kan användas.Du kommer att lära dig om dess delar, hur du ställer in den och varför du fortfarande använder det idag i saker som radioapparater, maskiner, bilar och mer.Det visar också hur det jämförs med andra liknande chips.Katalog

Vad är EPF8820ARC208-4?

De EPF8820ARC208-4 är en äldre FPGA -enhet från Flex 8000 -serien utvecklad av Altera, nu under Intel Programmerable Solutions Group.Den är designad med en CMOS SRAM-baserad arkitektur och tillhör en familj av rekonfigurerbara logikenheter som markerade en fas i programmerbar logikutveckling.Flex 8000-serien känns igen för sin mångsidiga logikcellstruktur och skalbar samtrafik, lämplig för allmän digital integration.EPF8820ARC208-4 faller specifikt in i en variant i mellanhastigheten i denna serie och sammankopplingsfunktioner.Den delar sin arkitektur med andra varianter för hastighetsklass som '2, '3 och -5, som främst skiljer sig åt i tidsresultatet.

Letar du efter EPF8820ARC208-4?Kontakta oss för att kontrollera nuvarande lager, ledtid och prissättning.

EPF8820ARC208-4 FUNKTIONER

• Flex 8000 arkitektur

EPF8820Arc208-4 är byggt på Alteras Flex 8000-arkitektur, som använder SRAM-baserad konfiguration för programmerbarhet i systemet.Det ger en kostnadseffektiv och flexibel lösning för medelstora logikdensitetsapplikationer.

• Logisk densitet

Den här enheten integrerar 672 logikelement och levererar cirka 8 000 användbara systemgrindar.Det erbjuder en lämplig balans mellan komplexitet och prestanda för inbäddad kontroll, limlogik och tillståndsmaskindesign.

• 5V Core med Multivolt ™ I/O -stöd

Driften på en 5V -leverans stöder enheten också 3,3V och 5V I/O -standarder med MULIVOLT ™ I/O -teknik.Detta gör det anpassningsbart för blandade spänningar och gränssnitt för äldre.

• Omprogrammerbar konfiguration i krets

EPF8820ARC208-4 är SRAM-baserad och stöder konfiguration i krets med externa seriella eller parallella proms.Det möjliggör snabba designuppdateringar och rekonfiguration utan att ta bort enheten från kretsen.

• FastTrack Interconnect Routing

Dess FastTrack Interconnect-struktur ger ett förutsägbart, höghastighets routingtyg.Denna arkitektur stöder effektiv logikplacering och tidskontroll, vilket möjliggör strömlinjeformad designprestanda.

• Bär och kaskadkedjor för aritmetik

Dedikerade bär- och kaskadkedjor förbättrar implementeringen av aritmetiska funktioner som tillägg och räknare.Dessa funktioner minskar logisk försening och förenklar konstruktionen av komplexa matematiska operationer.

• PCI -bussöverensstämmelse (Rev 2.2)

Den här enheten uppfyller PCI Local Bus Specification Revision 2.2, vilket gör den lämplig för användning i PCI-baserade system.Det stöder 5V-toleranta PCI-signalmiljöer.

• JTAG gränsskanningssupport

EPF8820ARC208-4 inkluderar inbyggd IEEE 1149.1 (JTAG) gränsskanningsfunktioner.Detta underlättar felsökning, styrelseprovning och verifiering i systemet utan att kräva ytterligare kretsar.

• Programmerbar svänghastighetskontroll

Dess utgångsdrivare har programmerbar SLEW -hastighetskontroll, vilket hjälper till att minimera växlingsbuller.Detta är fördelaktigt i höghastighetsdesign för signalintegritet.

• Lågkraft Standby-läge

Enheten är designad för effekteffektivitet och förbrukar mindre än 0,5 mA i standby -läge.Detta gör det möjligt för system att spara kraft under lediga eller inaktiva perioder.

• Driftstemperatur: 0 ° C till 70 ° C

Komponenten fungerar pålitligt inom ett kommersiellt temperaturområde från 0 ° C till 70 ° C.Det är idealiskt för allmänt användning i kontrollerade miljöer.

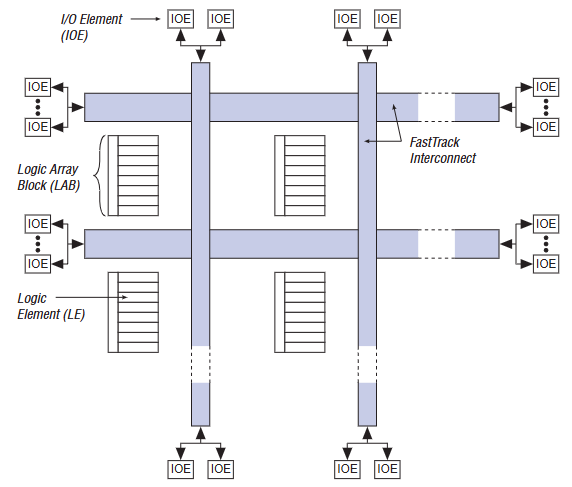

Flex 8000 blockdiagram

Diagrammet illustrerar den interna strukturen och hur FPGA bearbetar logik och anslutningar.I mitten finns de logiska arrayblocken (labb), som innehåller flera logikelement (LES).Dessa LE: er är programmerbara och kan konfigureras för att utföra ett brett utbud av logiska uppgifter, vilket stödjer både kombinerande och sekventiella mönster.Denna flexibilitet möjliggör anpassad implementering av digital krets.

Runt laboratorierna finns I/O -elementen (IOE), som hanterar kommunikation mellan FPGA och externa enheter.De stöder inmatnings-, utgångs- och dubbelriktade signaler medan de rymmer olika spänningsnivåer.Anslutning av alla delar är FastTrack Interconnect, ett höghastighetsrutningssystem som länkar laboratorier och IOE effektivt.Denna installation säkerställer snabb dataöverföring, smidig signalrutning och pålitlig prestanda över olika applikationer inom Flex 8000 -serien.

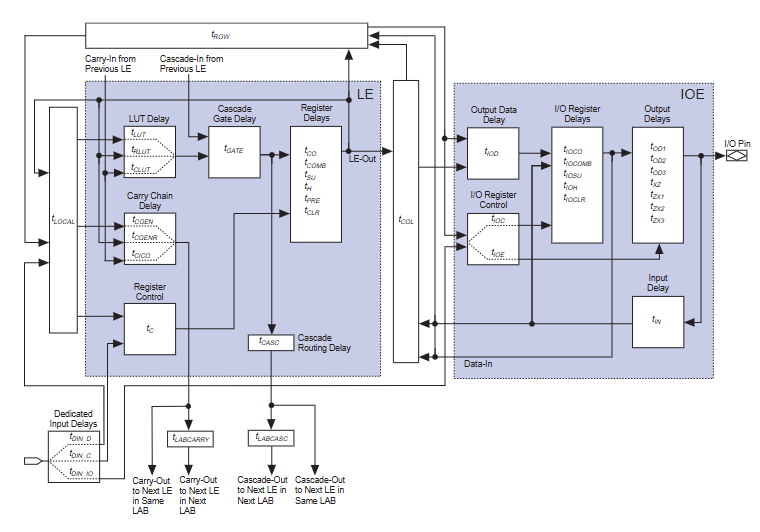

Flex 8000 tidsläge

Diagrammet belyser hur förseningar påverkar logikbehandling och signalflöde inom FPGA.Inuti varje logikelement (LE) bestämmer tidsfaktorer som uppslagstabell (LUT) fördröjning, fördröjning av kedjan och registrering av inställningar/hålltider hur snabbt logikoperationer svarar på ingångsförändringar.Dessa interna förseningar är viktiga för att upprätthålla korrekt och stabil drift, särskilt i snabbomkopplingskretsar.

För I/O -operationer visar tidsläget hur signaler uppför sig när de går in och lämnar FPGA.Nyckelpunkter inkluderar utgångsfördröjning, såväl som inställningar och hålltider, som definierar hur länge externa signaler måste vara stabila för korrekt datainspelning.Diagrammet beskriver också förseningar mellan anslutna LES, inklusive bär- och kaskadvägar, vilket påverkar flödet av logik över enheten.Sammantaget säkerställer dessa timingelement synkroniserade, pålitliga prestanda över Flex 8000 -arkitekturen.

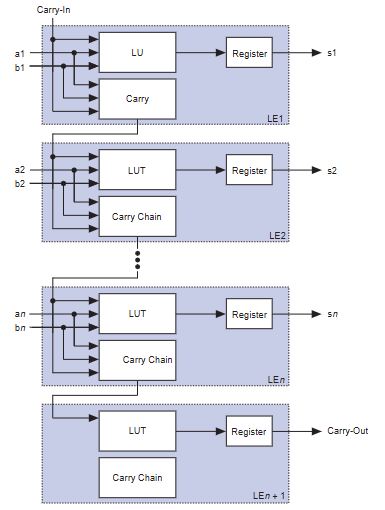

Flex 8000 transportkedja

Bärskedjan i EPF8820Arc208-4 Flex 8000 är utformad för att utföra snabba aritmetiska beräkningar genom att koppla flera logikelement (LES) tillsammans.Varje LE innehåller en uppslagstabell (LUT), en bärlogikkrets och ett register.Processen börjar med att en inlärningssignal kommer in i den första LE (LE1), som tillsammans med ingångar A1 och B1 producerar en SUM-utgång (S1) och en cross-signal.

Denna bärsignal överförs sedan direkt till nästa LE i kedjan (LE2, LE3, och så vidare), vilket gör att varje LE kan beräkna sin egen sume -utgång (S2 till SN) med sina ingångar och den inkommande bärningen.Den sista LE i sekvensen genererar den slutliga utvärderingssignalen och slutför operationen.Denna bärkedjestruktur möjliggör snabbt, effektivt tillägg, idealiskt för byggdimlar, räknare och annan aritmetisk baserad logik i Flex 8000-arkitekturen.

EPF8820ARC208-4 Specifikationer

|

Typ |

Parameter |

|

Tillverkare |

Altera/intel |

|

Serie |

Flex 8000 |

|

Förpackning |

Bricka |

|

Delstatus |

Föråldrad |

|

Antal laboratorier/clbs |

84 |

|

Antal logikelement/celler |

672 |

|

Antal I/O |

152 |

|

Antal grindar |

8000 |

|

Spänning - försörjning |

4.75V ~ 5.25V |

|

Monteringstyp |

Ytfäste |

|

Driftstemperatur |

0 ° C ~ 70 ° C (TA) |

|

Förpackning / fodral |

208-bfqfp exponerad pad |

|

Leverantörspaket |

208-RQFP (28x28) |

EPF8820ARC208-4 Applikationer

1. Digital signalbehandling (DSP) och datatvägskontroll

EPF8820ARC208-4 är väl lämpad för att implementera anpassade DSP-funktioner på grund av dess måttliga logikdensitet och effektiv routingarkitektur.Den kan hantera data-path-manipulation för operationer som filtrering, modulering och transformation av höghastighets digitala signaler.

2. Anpassat bussgränssnitt och avlastning av coprocessor

Med sitt stora antal I/O -stift och Multivolt ™ -stöd används detta FPGA ofta för att designa anpassade perifera gränssnitt eller brokompatibla logiknivåer.Det fungerar också som en medprocessor som avlastar repetitiva kontroller eller datahanteringsuppgifter från huvudprocessorn.

3. Programvarudefinierad radio- och kommunikationsbehandling

Enhetens flexibilitet och förmåga att omprogrammeras gör den idealisk för applikationer som programvarudefinierad radio (SDR), där moduleringsscheman eller protokoll kan ändras.Det kan dynamiskt hantera kodning, avkodning och signalhantering över kommunikationslager.

4. ASIC -prototyper och hårdvaruemulering

EPF8820ARC208-4 används vanligtvis under prototypfasen för ASIC-utveckling.Dess omprogrammerbara arkitektur möjliggör snabb validering, testning och tidpunktssimulering av komplexa digitala mönster innan de förbinder sig till kisel.

5. Röstigenkänning och krypteringsmotorer

Denna FPGA kan implementera medelstora komplexitetslogik som röstigenkänningsledningar och kryptografiska algoritmer.Närvaron av bärkedjor och registrerade I/OS säkerställer snabb beräkning och signalbehandling med låg latens som krävs för sådana applikationer.

6. Industriella kontroll- och instrumenteringssystem

De förutsägbara tidpunkten, stora fanout -synkronkontroller och flexibla logikblock gör denna FPGA lämplig för industriella automatiseringssystem.Det används ofta vid programmerbar timing, statsmaskinerkontroll och signalkonditioneringskretsar.

7. Aerospace and Defense Embedded Systems

Denna enhet används inom flyg- och försvarselektronik där konfigurationsflexibilitet och tillförlitlig drift i kontrollerade miljöer behövs.Den stöder säker firmware-lastning och erbjuder låg standby-kraft, som gynnar uppdragskritiska applikationer.

8. Automotive Electronic Modules

I bilelektronik kan EPF8820Arc208-4 hittas i kontrollmoduler som hanterar logiköversättning, diagnostik eller dataaggregering mellan sensorer och centrala ECU: er.Dess omkonfigurerbara karaktär tillåter uppdateringar och förbättringar även efter distributionen.

9. Telekommunikationsomkoppling och protokollhantering

I telekomsystem stöder denna FPGA omkopplingslogik, protokollhantering och tidtagning.Den kan anpassa sig till olika signalstandarder, vilket säkerställer kompatibilitet och uppgraderbarhet i dynamiska kommunikationsnätverk.

EPF8820ARC208-4 Liknande delar

Här är en jämförelsetabell över EPF8820Arc208-4 och dess mest relevanta liknande delar från samma flex8000-familj:

|

Artikelnummer |

Hastighetsgrad |

Pakettyp |

I/O -stift |

Logikelement |

Temperaturgrad |

|

EPF8820ARC208-4 |

–4 (baslinje) |

208-stift QFP |

152 |

672 |

Kommersiell |

|

EPF8820ARC208-2 |

–2 (långsammare) |

208-stift QFP |

152 |

672 |

Kommersiellt (0–70 ° C) |

|

EPF8820ARC208-3 |

–3 (medium) |

208-stift QFP |

152 |

672 |

Kommersiell |

|

EPF8820ARC208-5 |

–5 (snabbare) |

208-stift QFP |

152 |

672 |

Kommersiell |

|

EPF8820AQC208-4 |

–4 |

208-stift QFP (AQC) |

152 |

672 |

Kommersiell |

|

EPF8820ari208-4H |

–4 |

208-stift QFP |

152 |

672 |

Industriell (–40–85 ° C) |

EPF8820ARC208-4 Programmeringssteg

1. Generera konfigurationsfilen

Börja med att skapa konfigurationsfilen med Alteras utvecklingsprogramvara som Max+Plus II eller Quartus.Denna fil, vanligtvis cirka 16 kb i storlek, innehåller den kompletta bitströmmen som behövs för att definiera logik och routing för EPF8820Arc208-4.

2. Välj konfigurationsschema

Välj en lämplig konfigurationsmetod baserad på systemkrav: antingen aktiv serie/parallell (där FPGA kontrollerar lastning) eller passiv serie/parallell (där en extern styrenhet hanterar konfiguration).Passiva metoder är idealiska för system som kräver omprogrammering eller dynamiska uppdateringar.

3. Ställ in hårdvaruanslutningar

Anslut nödvändiga konfigurationslinjer som NCONFIG, CONF_DONE, DCLK och data0 mellan FPGA och din valda konfigurationsminnesenhet (t.ex. EPC1, EPC1213).Se till att pull-up-motstånd och klockkällor är korrekt konfigurerade för att matcha det valda konfigurationsläget.

4. Power-on-initiering

När systemet drivs upp eller NConfig påstås, går FPGA in i konfigurationsläge och placerar allt I/OS i ett Tri-State-tillstånd.Enheten är nu redo att acceptera konfigurationsdata baserat på ledningssystemet du implementerade.

5. Lastkonfigurationsdata

I aktivt läge hämtar FPGA data direkt från EPROM med sin interna oscillator.I passivt läge tillhandahåller en värdprocessor eller konfigurationskontroller data, och processen slutförs när conf_done -signalen blir hög.

6. Intern initialisering och övergång till användarläge

När bitströmmen är fullastad och konf_done har hävdats utför FPGA intern initialisering, sätter register och möjliggör användare I/O.Enheten börjar sedan utföra den logiska designen programmerad i den.

7. Valfri rekonfiguration

Du kan utlösa en rekonfigurationscykel genom att dra NConfig Low, som återställer enheten och återgår till konfigurationsläget.Detta möjliggör snabba uppdateringar i systemet eller återhämtning av logik, med hela omprogrammeringsprocessen som vanligtvis är klar i under 100 millisekunder.

EPF8820ARC208-4 Fördelar

• Balanserad hastighetskvalitetsval

EPF8820Arc208-4 erbjuder en idealisk balans mellan prestanda och kostnad, vilket gör det snabbare än lägre klass –2 eller –3 varianter samtidigt som man undviker den högre prispunkten för –5 hastighetskvaliteten.Detta gör det möjligt att uppfylla tidskraven utan att betala för mycket för oanvänd utrymme.

• Förutsägbara routingförseningar för kontrolllogik

Tack vare dess finkorniga horisontella routing och konsekventa fördröjningsvägar ger EPF8820Arc208-4 utmärkt förutsägbarhet för timing.Detta är användbart vid kontrollorienterade eller statsmaskin-tunga mönster

• Snabbfältrekonfiguration

Dess SRAM-baserade struktur möjliggör rekonfiguration i mindre än 100 millisekunder, vilket möjliggör uppdateringar av firmware och fallback-logik i live-system.Detta är värdefullt i avlägsna eller uppdragskritiska applikationer där driftstopp måste minimeras.

• Kostnadseffektiv

För applikationer som kräver cirka 8 000 systemgrindar ger EPF8820Arc208-4 precis rätt mängd logik utan omkostnaderna för större moderna FPGA: er.Detta håller BOM -kostnaderna låga medan de uppfyller funktionalitetskraven.

• Förenklad integration med blandad spänningar

Med inbyggt stöd för både 3,3V och 5V I/O-signalering förenklar enheten systemdesign när den gränssnittet med äldre TTL- eller blandade spänningskomponenter.Detta eliminerar behovet av ytterligare nivåskiftare, vilket sparar kortutrymme och kostnad.

EPF8820ARC208-4 Förpackningsdimensioner

• Pakettyp: 208-stifts RQFP (Rectangular Quad Flat Package)

• Kroppsstorlek (D × E): 30,60 mm × 30,60 mm

• Paketöversikt (D1 × E1): ungefär 28,00 mm × 28,00 mm

• Blyplan (e): 0,50 mm

• Blylängd (L): 0,60 mm typiskt (intervall: 0,45 mm till 0,75 mm)

• Ledningsbredd (b): 0,17 mm typiskt (intervall: 0,17 mm till 0,27 mm)

• Blyvinkel: 0 ° till 8 °

• Monteringstyp: Ytmontering

EPF8820ARC208-4 Tillverkare

EPF8820ARC208-4 tillverkas av Anläggningsföretag, ett banbrytande företag inom program för programmerbara logikenheter (PLD) och fältprogrammerbara grindarrayer (FPGA).Alteras utvecklade ursprungligen Flex 8000-familjen, till vilken den här enheten tillhör, och erbjuder en rekonfigurerbar arkitektur skräddarsydd för logiska applikationer i mitten av densitet.2015 förvärvades altera av Intel Corporationoch produkten fortsatte att stödjas under Intels programmerbara lösningsgrupp.Men 2024–2025 återupprättade Intel Alta som ett fristående varumärke, vilket bekräftar sitt fokus på FPGA-utveckling och långsiktigt stöd.Medan EPF8820Arc208-4 officiellt klassificeras som föråldrad, förblir dess tillverkningsarv bundet till Alteras arv att leverera tillförlitliga, flexibla och allmänt antagna programmerbara logiklösningar.

Slutsats

EPF8820ARC208-4 är ett flexibelt och pålitligt chip som erbjuder en bra blandning av hastighet, funktioner och kostnad.Det fungerar bra i många olika system eftersom det kan omprogrammeras, stöder olika spänningar och hanterar matematik- och kontrolluppgifter snabbt.Dess design hjälper till att se till att signaler rör sig smidigt och exakt.Även om det nu betraktas som en äldre eller avvecklad del, är det fortfarande användbart i system som behöver stabil prestanda och inte enkelt kan byta till nyare chips.Detta gör det till ett smart alternativ för uppdateringar, reparationer eller långsiktigt stöd för äldre elektronik.

Om oss

ALLELCO LIMITED

Läs mer

Snabb förfrågan

Skicka en förfrågan, vi svarar omedelbart.

Vanliga frågor [FAQ]

1. Kräver EPF8820Arc208-4 externt konfigurationsminne för att starta upp?

Ja, den använder externa seriella eller parallella proms som EPC1 eller EPC1213 för att ladda konfigurationsdata under systeminitiering eller återställning.

2. Hur vet jag om min befintliga kortdesign stöder EPF8820Arc208-4-konfigurationsläget?

Kontrollera ditt schema för nödvändiga stift som NConfig, Conf_Done, DCLK och Data0.Se också till att ditt konfigurationsminne (som EPC1 eller EPC1213) matchar den valda seriella eller parallella konfigurationsmetoden.

3. Kan jag utföra partiell rekonfiguration på EPF8820Arc208-4?

Nej, EPF8820ARC208-4 stöder inte partiell rekonfiguration.Eventuella uppdateringar eller logiska ändringar kräver en fullständig bitström omlastning via standardkonfigurationscykeln.

4. Finns det någon risk för bitströmskorruption under uppstart?

Ja, om konfigurationstiming eller signalintegritet inte upprätthålls ordentligt, kan bitströmskorruption uppstå.Se till att ren effekt sekvensering och korrekt frikoppling nära FPGA och konfigurationslinjer.

5. Kan jag använda EPF8820ARC208-4 för kryptografiska funktioner eller säker bearbetning?

Även om det inte är säkerhetshärdat, är enheten lämplig för att implementera anpassad kryptografisk logik som grundläggande krypteringsmotorer eller nyckelhantering, men den saknar inbyggda säkra funktioner som finns i moderna FPGA: er.

Hur EPM7064AEFC100-10 kan förenkla din logikdesign

på 2025/07/14

LC5768MC-75F256C CPLD: Funktioner, specifikationer, fördelar och applikationer

på 2025/07/10

Populära inlägg

-

Komplexa instruktionsuppsättningsdatorer: Hur de ändrade datoranvändning?

på 8000/04/18 147773

-

USB-C-pinout och funktioner

på 2000/04/18 112011

-

Använda Xilinx Unified Simulation Primitives: En omfattande guide till FPGA -design och simulering

på 1600/04/18 111351

-

Strömförsörjningsspänningar i elektronik: Betydelsen av VCC, VDD, VEE, VSS och GND

på 0400/04/18 83769

-

RJ45 -anslutningsguide: Pinout, ledningar, kabeltyper och användningar

på 1970/01/1 79565

-

Den ultimata guiden för trådfärgkoder i moderna elektriska system

Hur våra elektriska system använder färger är inte bara för utseende.Varje trådfärg indikerar nu en specifik funktion, vilket gör det lättare att identifiera och hantera elektriska komponenter korr...på 1970/01/1 66960

-

Purge Valve Guide: Funktion, symtom, testning och ersättning för optimal motorprestanda

Purge -ventilen är en viktig del av bilens system som hjälper till att hålla luften ren genom att hantera bränsleångor innan de kan fly in i atmosfären.Detta hjälper inte bara miljön genom att mins...på 1970/01/1 63100

-

Kvalitet (Q) Faktor: Ekvationer och applikationer

Kvalitetsfaktorn, eller 'Q', är viktig när man kontrollerar hur väl induktorer och resonatorer arbetar i elektroniska system som använder radiofrekvenser (RF).'Q' mäter hur väl en krets minimerar e...på 1970/01/1 63040

-

Uppnå toppprestanda med den maximala kraftöverföringssatsen

Den maximala kraftöverföringssatsen förklarar hur energi från en källa, till exempel ett batteri eller generator, flyter till en ansluten belastning.Det visar det exakta tillståndet där lasten får ...på 1970/01/1 54097

-

A23 -batterispecifikationer och kompatibilitet

A23-batteriet är ett litet, cylinderformat batteri med högspänning.Även kallad 23A, 23AE eller MN21, den körs vid 12 volt och mycket högre än AA- eller AAA -batterier.Dess speciella design...på 1970/01/1 52184