EPM7064STC100-7 CPLD: Funktioner, applikationer och programmeringsguide i systemet

EPM7064STC100-7 är ett kraftfullt chip från Intels Max® 7000S-serie, utformad för att hantera komplexa uppgifter i elektroniska enheter.Den här guiden diskuterar huvudfunktionerna och användningarna av EPM7064STC100-7, och betonar dess förmåga att enkelt omprogrammeras, dess snabba drift och dess flexibla design.Idealisk för många olika tekniker, från små prylar till stora industrimaskiner, är detta chip en viktig del för att bygga avancerade digitala kretsar.Katalog

EPM7064STC100-7 Beskrivning

De EPM7064STC100-7 är en komplex programmerbar logikenhet (CPLD) från Intels Max® 7000S -serie.Den har 64 makroceller och 1 250 grindar, vilket hjälper till att bygga komplexa digitala kretsar.Detta chip går med en maximal hastighet på 166,7 MHz, med en signalfördröjning på 7,5 nanosekunder (NS).Den har 68 ingångs-/utgångsstift (I/O) som fungerar med 3,3V och 5V -logik, vilket gör det enkelt att använda i olika kretsar.En nyckelfunktion är dess 5.0V in-system-programmerbarhet (ISP) genom ett JTAG-gränssnitt (IEEE 1149.1).Detta innebär att du kan omprogrammera den utan att ta bort den från kretsen, underlätta testning och uppdateringar.Den finns i en 100-stifts tunn quad-platt-förpackning (TQFP), som är ett kompakt, ytmonteringspaket.Denna CPLD används i inbäddade system, digital signalbehandling, kommunikationsenheter och industriell automatisering.

Vi tillhandahåller komponenter av hög kvalitet och anpassade tjänster, så det är bäst att placera din bulkorder hos oss för pålitliga CPLD-lösningar.

EPM7064STC100-7 Funktioner

• Högdensitetslogik: EPM7064STC100-7 är designad med 64 makroceller och 1 250 användbara grindar, vilket gör det mycket lämpligt för att implementera komplexa logikfunktioner i digitala kretsar.Denna högdensitetsarkitektur gör det möjligt att skapa komplicerade logikkonstruktioner samtidigt som effektiviteten i programmerbara logikoperationer bibehålls.Den väloptimerade makrocellstrukturen säkerställer ett effektivt utnyttjande av tillgängliga resurser och stöder avancerade kombinations- och sekventiella logiska implementeringar.

• Snabb prestanda: EPM7064STC100-7 byggd för höghastighetsbehandling och fungerar med en maximal intern frekvens på 166,7 MHz, vilket möjliggör snabb exekvering av logikfunktioner.Dess förökningsfördröjning på 7,5 ns säkerställer minimal latens.Denna snabba växlingskapacitet förbättrar enhetens förmåga att hantera höghastighetsdatabehandling, signalkonditionering och kontrolluppgifter effektivt, vilket gör det till ett tillförlitligt val för krävande digitala system.

• Mångsidig I/O: Med 68 programmerbara ingångs-/utgångsstift erbjuder EPM7064STC100-7 exceptionell flexibilitet för integration i olika kretskonstruktioner.Genom att stödja både 3.3V och 5V logiknivåer tillåter den sömlös kompatibilitet med olika systemspänningar, vilket eliminerar behovet av ytterligare spänningsnivån.Denna anpassningsförmåga gör den väl lämpad för applikationer i miljöer med blandad spänningar, vilket säkerställer bred tillämpbarhet mellan inbäddade system, industriella kontroller och kommunikationsnätverk.

• Programmerbarhet i systemet (ISP): En av fördelarna med EPM7064STC100-7 är dess 5.0V in-systemprogrammerbarhet (ISP), underlättad genom en IEEE STD.1149.1 JTAG -gränssnitt.Denna funktion gör det möjligt att omprogrammera och ändra logikfunktioner utan att tappa ut eller fysiskt ta bort enheten, förenkla underhåll, felsökning och iterativ utveckling.ISP -kapaciteten minskar driftsstoppet och förbättrar flexibiliteten i firmwareuppdateringar, vilket gör det ovärderligt för dynamiska och rekonfigurerbara digitala mönster.

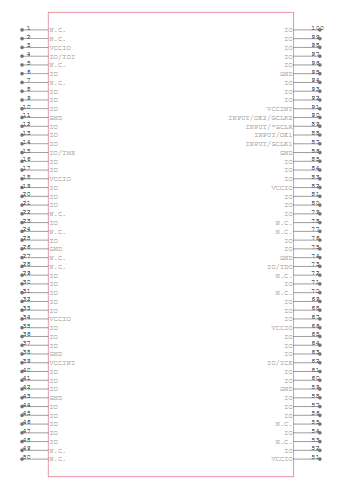

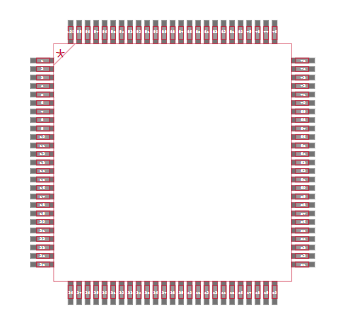

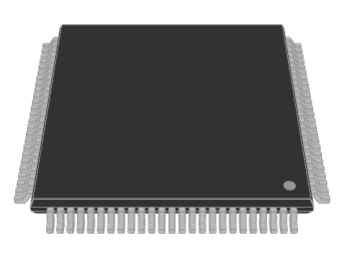

EPM7064STC100-7 CAD-modeller

EPM7064STC100-7 Symbol

EPM7064STC100-7 FOTPRINT

EPM7064STC100-7 3D-modell

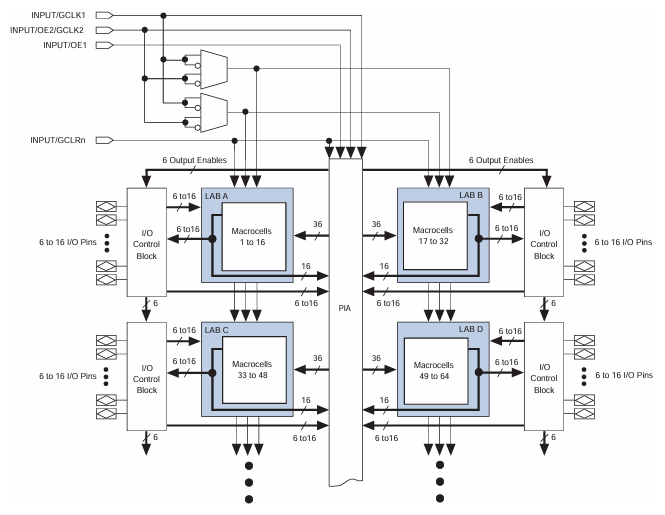

EPM7064STC100-7 blockdiagram

De EPM7064STC100-7 blockdiagram Visar hur chipets logikelement är anslutna och kontrollerade.Den har fyra logiska arrayblock (labb), märkt A, B, C och D, var och en innehåller 16 makroceller.Dessa makroceller utför logikfunktioner, och de ansluter sig genom en programmerbar interconnect -array (PIA), som möjliggör flexibel routing av signaler.Varje laboratorium är länkat till ett I/O -kontrollblock och hanterar upp till 16 ingångs-/utgångsstift per labb.Diagrammet visar också globala styrsignaler (GCLK1, GCLK2, OE1 och GCLRN) som hjälper till att hantera klock- och återställningsfunktioner för chipet.Vissa logiska grindar bearbetar dessa signaler innan de når olika delar av systemet.Utformningen av EPM7064STC100-7 gör det möjligt att användas i olika programmerbara logiska applikationer, såsom tillståndsmaskiner, adressavkodning och andra anpassade digitala kretsar.Dess flexibla sammankopplingar säkerställer effektivt signalflöde och tillförlitlig drift.

EPM7064STC100-7 Specifikationer

|

Typ |

Parameter |

|

Tillverkare |

Altera/intel |

|

Serie |

Max® 7000s |

|

Förpackning |

Bricka |

|

Delstatus |

Föråldrad |

|

Programmerbar typ |

I systemprogrammerbar |

|

Fördröjningstid TPD (1) Max |

7,5 ns |

|

Spänningsförsörjning - intern |

4.75V ~ 5.25V |

|

Antal logikelement/block |

4 |

|

Antal makroceller |

64 |

|

Antal grindar |

1250 |

|

Antal I/O |

68 |

|

Driftstemperatur |

0 ° C ~ 70 ° C (TA) |

|

Monteringstyp |

Ytfäste |

|

Förpackning / fodral |

100-TQFP |

|

Leverantörspaket |

100-TQFP (14x14) |

|

Basproduktnummer |

EPM7064 |

EPM7064STC100-7 in-system-programmeringssekvens (ISP)

EPM7064STC100-7, en del av Max 7000S CPLD-familjen, följer en sexstegs i systemprogrammeringssekvens (ISP) för att säkerställa korrekt konfiguration.Denna process gör det möjligt för dig att programmera enheten utan att ta bort den från kretskortet.ISP -processen innebär att du flyttar instruktioner, adresser och data via TDI (testdata i) -stiftet medan du hämtar svar via TDO (Test Data Out).

Det första steget, Ange ISP, säkerställer att I/O -stift övergår smidigt från användarläge till ISP -läge och kräver cirka 1 ms.Detta följs av Kontrollera ID, där kisel -ID för enheten läses för att bekräfta rätt mål.Därefter Bulkrader Stegförskjutningar i raderingsinstruktioner och tillämpar en 100ms raderingspuls och rensar alla befintliga data i EEPROM -cellerna.De Programmera Steg följer, där adresser och data i följd avmarkeras i enheten och tillämpar programmeringspulser för att konfigurera EEPROM -cellerna.Varje adress måste programmeras individuellt, vilket gör detta steg tidskrävande beroende på antalet EEPROM-celler i enheten.

När programmeringen är klar, Kontrollera Steg säkerställer att data har lagrats korrekt.Här appliceras läspulser på EEPROM -celler, och de hämtade data jämförs med de förväntade värdena.Om avvikelser hittas kan omprogrammering vara nödvändig.Slutligen, Utgångs ISP Steg säkerställer att I/O -stift övergår till användarläge och kräver ytterligare 1 ms.Den totala programmerings- eller verifieringstiden påverkas av två huvudfaktorer: pulstid, som krävs för EEPROM -radering, programmering och läsoperationer och skiftningstid, vilket beror på TCK -frekvensen (testklockan) och antalet cykler som krävs för att överföra instruktioner, adresser och data.Eftersom olika ISP-kapabla enheter har ett varierande antal EEPROM-celler är både totala fasta och variabla tider unika för varje enhet.Den totala ISP -tiden kan beräknas som en funktion av TCK -frekvens, antalet målenheter och EEPROM -arkitekturen.

EPM7064STC100-7 Applikationer

Inbäddade system

EPM7064STC100-7 används allmänt i inbäddade systemapplikationer, där den fungerar som en flexibel programmerbar logiklösning för att kontrollera olika kringutrustning, bearbeta signaler och implementera anpassade protokoll.Dess förmåga att gränssnitt med mikrokontroller och sensorer gör det möjligt att optimera systemets prestanda och samtidigt bibehålla ett kompakt fotavtryck.Med sin höghastighetsdrift och låg effektförbrukning är det ett utmärkt val för inbäddade applikationer som kräver tillförlitlighet och effektivitet.

Digital signalbehandling (DSP)

Vid digital signalbehandling spelar EPM7064STC100-7 en roll i implementering av filter, signalmodulering och olika matematiska funktioner.Dess snabba omkopplingshastigheter och låg fördröjningsfördröjning gör den lämplig för att hantera högfrekventa databehandlingsuppgifter, vilket säkerställer minimal latens vid signalomvandling och manipulation.Det används vanligtvis vid ljudbehandling, telekommunikation och radarsystem.

Datakommunikation

EPM7064STC100-7 används i stor utsträckning inom nätverks- och datakommunikationssystem på grund av dess förmåga att hantera logikintensiva operationer som datarrutning, buffring och felkorrigering.Dess programmerbara I/O -kapacitet gör det möjligt att anpassa sig till olika kommunikationsprotokoll, vilket gör det till en värdefull komponent i Ethernet -switchar, routrar och telekommunikationsinfrastruktur.Dess stöd för programmerbarhet i systemet (ISP) möjliggör också fältuppdateringar, vilket förbättrar anpassningsbarhet i dynamiska nätverksmiljöer.

Industriautomation

Industriella tillämpningar kräver hög tillförlitlighet, hållbarhet och låg effektförbrukning, vilket gör EPM7064STC100-7 till ett föredraget val för programmerbara logikstyrenheter (PLC), motorstyrningssystem och automatiserad testutrustning.Med sin JTAG-baserade programmerbarhet i systemet ger det möjligheten att förfina automatiseringsprocesser utan att kräva fysisk borttagning eller omformning.Dess mångsidighet i spänningskompatibilitet gör den också lämplig för gränssnitt med ett brett utbud av sensorer och ställdon som används i industriella miljöer.

EPM7064STC100-7 Liknande delar

EPM7064STC100-7 Fördelar

Programmerbarhet i systemet (ISP)

En av de största fördelarna med EPM7064STC100-7 är dess förmåga att omprogrammeras medan den fortfarande är monterad i systemet.Detta eliminerar behovet av att ta bort chipet för uppdateringar, minska underhållstiden och förbättra effektiviteten.Du kan implementera designändringar utan att avbryta produktionen, vilket gör det till en kostnadseffektiv lösning för långsiktiga projekt.

Höghastighetsprestanda

Enheten stöder en hög intern driftsfrekvens upp till 166,7 MHz, vilket möjliggör snabb databehandling och responstider.Detta gör det idealiskt för applikationer som kräver signalbehandling, logikstyrning och höghastighetsgränssnitt, vilket säkerställer smidigare och mer pålitlig systemdrift.

Mångsidig I/O -stöd

Med upp till 68 konfigurerbara I/O-stift och kompatibilitet med flera spänningsnivåer (3,3V, 5V och toleranta alternativ för 2,5V, 3,3V och 5V) erbjuder EPM7064STC100-7 flexibilitet i systemdesign.Det möjliggör sömlös integration i olika kretsar och stöder miljöer med blandade spänningar, vilket minskar kompatibilitetsproblemen med andra komponenter.

Tillförlitlig drift över miljöer

EPM7064STC100-7 är utformad för att fungera inom ett temperaturområde från 0 ° C till 70 ° C.Denna tillförlitlighet gör det till ett föredraget val för applikationer där miljöstabilitet krävs, såsom industriell automatisering, telekommunikation och inbäddade kontrollsystem.

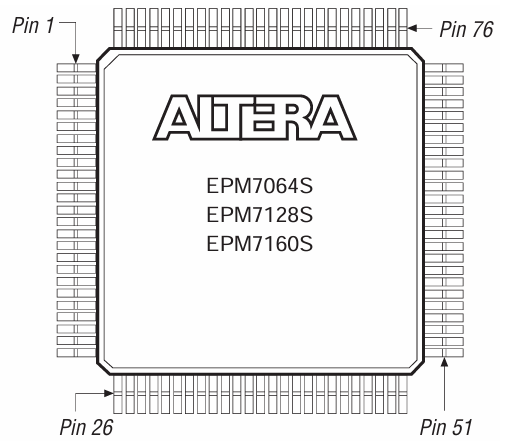

EPM7064STC100-7 PACKET PIN-OUT DIAGRAM

EPM7064STC100-7 är en CPLD (komplex programmerbar logikenhet) från Alteras Max 7000S-serie, inrymt i ett 100-stifts tunn quad-platt-paket (TQFP-100).Denna pakettyp är utformad för ytmonterade applikationer, vilket erbjuder en balans mellan hög stiftdensitet och kompakt storlek.De pin-out-diagram Följer ett moturs numreringsschema, med stift 1 beläget i det övre vänstra hörnet av paketet.Rörande moturs, de första 25 stiften upptar vänster sida, stift 26 till 50 är placerade längs underkanten, stift 51 till 75 fortsätter längs höger sida och stift 76 till 100 är fördelade längs övre kanten.De TQFP-100-paket Har tunna ledningar som sträcker sig utåt från alla fyra sidor av den platta, fyrkantiga kroppen.Denna design förbättrar ytmonteringskompatibiliteten samtidigt som man bibehåller adekvat stiftavstånd för enkel lödning och montering.Ledningsplanen (avståndet mellan angränsande stift) är vanligtvis 0,5 mm, vilket optimerar signalintegritet samtidigt som det totala fotavtrycket minimeras.

EPM7064STC100-7 Tillverkare

EPM7064STC100-7 är en CPLD (komplex programmerbar logikanordning) som ursprungligen utvecklats av Altera, ett halvledarföretag känt för sina programmerbara logiklösningar.2015, Intel förvärvade Altera, integrera sina FPGA- och CPLD -produktlinjer i Intels programmerbara Solutions Group (PSG).Sedan dess har EPM7064STC100-7 märkts under Intel, även om den har markerats som föråldrad.Intel, som tillverkaren, upprätthöll arvetstödet för Max® 7000S Series CPLD, inklusive denna modell, samtidigt som den gradvis flyttade fokus mot moderna FPGA och programmerbara logiktekniker.

Slutsats

EPM7064STC100-7 samlar komplexa funktioner, snabba prestanda och enkla uppdateringar i ett chip, vilket bevisar dess värde i att utmana digitala inställningar.Den här guiden har visat hur den fungerar, vad den används för och hur den passar in i olika elektroniska system.Det hjälper till att få enheter att köra smidigt och effektivt, vilket bevisar att det fortfarande är mycket användbart för många applikationer.Den här guiden ger en tydlig bild av hur EPM7064STC100-7 kan hjälpa till att förbättra elektroniska mönster och systemoperationer effektivt.

Datablad pdf

EPM7064STC100-7 Datablad:

Om oss

ALLELCO LIMITED

Läs mer

Snabb förfrågan

Skicka en förfrågan, vi svarar omedelbart.

Vanliga frågor [FAQ]

1. Hur påverkar 7,5NS-förökningsfördröjningen av EPM7064STC100-7 PROPRESTERING?

En förökningsfördröjning på 7,5NS säkerställer signalbehandling med låg latens, vilket gör denna CPLD lämplig för höghastighetsapplikationer såsom digital signalbehandling (DSP), kommunikationssystem och industriell automatisering som kräver exakt tidskontroll.

2. Kan EPM7064STC100-7 programmeras med moderna utvecklingsverktyg?

Ja, det kan programmeras med Intels programvara Quartus II (tidigare Alta Quartus) tillsammans med en lämplig JTAG -programmerare.Support för äldre CPLD som EPM7064STC100-7 kan emellertid vara begränsat i nyare Quartus-versioner, så du kan behöva använda Legacy-versioner som Quartus II 13.0 SP1, som fortfarande stöder Max® 7000S-serieenheter.

3. Stödjer EPM7064STC100-7 miljöer med blandade spänningar?

Ja, det stöder både 3.3V och 5V logiknivåer, vilket gör det kompatibelt med ett brett utbud av digitala kretsar.Denna flexibilitet är användbar för att gränssnitts Legacy 5V-komponenter med moderna 3.3V-system utan ytterligare nivåskiftande kretsar.

4. Vad är den bästa metoden för felsökning av en EPM7064STC100-7-baserad design?

För att felsöka kan du använda Quartus Signaltap II Logic Analyzer eller externa oscilloskop och logiska analysatorer för att övervaka signaler.Om felsökning av JTAG -programmeringsproblem, se till att TDI-, TDO-, TCK- och TMS -anslutningar är korrekta och att du använder en kompatibel USB -blaster eller byteblasterMV -programmerare.

5. Kan jag programmera EPM7064STC100-7 utan att ta bort det från mitt kretskort?

Ja.5.0V-programmbarheten i systemet (ISP) via JTAG (IEEE 1149.1) låter dig omprogrammera enheten medan den förblir i systemet.Detta gör firmware -uppdateringar, felsökning och testning mycket effektivare jämfört med traditionella CPLD: er.

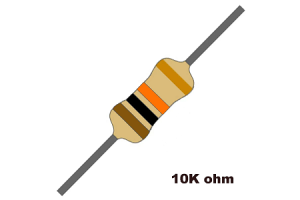

Komplett guide till 10K -motståndet: färgkod, applikationer och kretsanvändningar

på 2025/03/10

Kondensatorer kontra batterier: Vilket är bäst för dina energibehov?

på 2025/03/7

Populära inlägg

-

Komplexa instruktionsuppsättningsdatorer: Hur de ändrade datoranvändning?

på 8000/04/18 147766

-

USB-C-pinout och funktioner

på 2000/04/18 111994

-

Använda Xilinx Unified Simulation Primitives: En omfattande guide till FPGA -design och simulering

på 1600/04/18 111351

-

Strömförsörjningsspänningar i elektronik: Betydelsen av VCC, VDD, VEE, VSS och GND

på 0400/04/18 83758

-

RJ45 -anslutningsguide: Pinout, ledningar, kabeltyper och användningar

på 1970/01/1 79552

-

Den ultimata guiden för trådfärgkoder i moderna elektriska system

Hur våra elektriska system använder färger är inte bara för utseende.Varje trådfärg indikerar nu en specifik funktion, vilket gör det lättare att identifiera och hantera elektriska komponenter korr...på 1970/01/1 66952

-

Purge Valve Guide: Funktion, symtom, testning och ersättning för optimal motorprestanda

Purge -ventilen är en viktig del av bilens system som hjälper till att hålla luften ren genom att hantera bränsleångor innan de kan fly in i atmosfären.Detta hjälper inte bara miljön genom att mins...på 1970/01/1 63096

-

Kvalitet (Q) Faktor: Ekvationer och applikationer

Kvalitetsfaktorn, eller 'Q', är viktig när man kontrollerar hur väl induktorer och resonatorer arbetar i elektroniska system som använder radiofrekvenser (RF).'Q' mäter hur väl en krets minimerar e...på 1970/01/1 63028

-

Uppnå toppprestanda med den maximala kraftöverföringssatsen

Den maximala kraftöverföringssatsen förklarar hur energi från en källa, till exempel ett batteri eller generator, flyter till en ansluten belastning.Det visar det exakta tillståndet där lasten får ...på 1970/01/1 54094

-

A23 -batterispecifikationer och kompatibilitet

A23-batteriet är ett litet, cylinderformat batteri med högspänning.Även kallad 23A, 23AE eller MN21, den körs vid 12 volt och mycket högre än AA- eller AAA -batterier.Dess speciella design...på 1970/01/1 52176