EPM7192SQC160-15 CPLD: Funktioner, pinout, programmering och applikationer

Den här guiden talar om EPM7192SQC160-15, ett programmerbart logikchip från Max 7000S-familjen.Det förklarar vad chipet kan göra, hur det fungerar och var det kan användas.Det visar hur chipet är byggt inuti, vad varje stift gör och hur det ansluter till andra delar.Guiden innehåller också var detta chip kan användas, hur man programmerar det steg för steg, vilka andra liknande chips finns och vem gör det.Katalog

Vad är EPM7192SQC160-15?

De EPM7192SQC160-15 är en mellanklass CPLD (komplex programmerbar logikenhet) från Max 7000S-familjen, gjord för tillförlitlig digital logikkontroll i inbäddade och industriella system.Detta chip erbjuder 192 makroceller och cirka 3 750 logiska grindar, vilket ger tillräckligt med kapacitet för att hantera måttliga logikuppgifter.Det inkluderar 124 I/O -stift och körs på 5V -tillförsel, med multivolt I/O -stöd för att gränssnittet med både 3.3V och 5V logiksystem.Dess programmerbara EEPROM-baserade arkitektur i systemet innebär att du kan omprogrammera den direkt i din krets med JTAG, utan att behöva extra komponenter eller externt minne.Med en hastighetsgrad –15 stöder den systemklockfrekvenser upp till cirka 76,9 MHz, vilket erbjuder snabb och konsekvent timingprestanda för omfattande digitala applikationer.Max 7000S -familjen är känd för sin solida prestanda, EEPROM -minne och flexibel spänningsdrift.

Letar du efter EPM7192SQC160-15?Kontakta oss för att kontrollera nuvarande lager, ledtid och prissättning.

EPM7192SQC160-15 CAD-modeller

EPM7192SQC160-15 Symbol

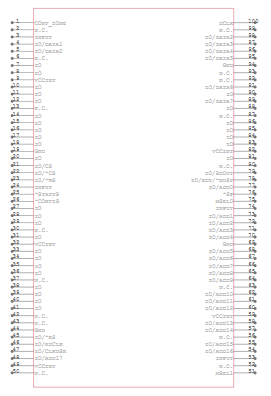

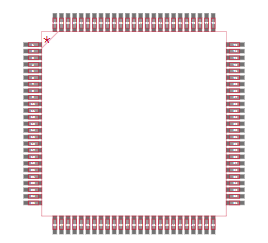

EPM7192SQC160-15 fotavtryck

EPM7192SQC160-15 3D-modell

EPM7192SQC160-15 Funktioner

192 Macroceller: Enheten innehåller 192 makroceller, som fungerar som de kärnprogrammerbara elementen.Dessa makroceller kan konfigureras för att implementera ett brett utbud av kombinations- och sekventiella logiska funktioner som krävs i digitala mönster.

Cirka 3 750 logiska grindar: Det erbjuder en ekvivalent logikkapacitet på cirka 3 750 grindar, vilket gör den lämplig för medelkomplexitetskontrolllogik, tillståndsmaskiner eller limlogik i inbäddade system.

Programmerbarhet i systemet via JTAG: Den har EEPROM-baserat minne som möjliggör omprogrammering direkt i systemet med hjälp av ett standard JTAG-gränssnitt, som stöder både IEEE 1149.1 och IEEE 1532-standarder.

Maximal frekvens upp till 125 MHz: Den interna logiken kan fungera vid klockhastigheter som når 125 MHz, vilket möjliggör snabb bearbetning för tidskänsliga applikationer.

Förökningsfördröjning på 7,5 ns: Chipet erbjuder en låg förökningsfördröjning på cirka 7,5 nanosekunder, vilket säkerställer snabb signalrespons från ingång till utgång.

Stöder 5V leverans med multivolt I/O: Enheten körs på en 5V-kärntillförsel och stöder multivolt I/O, vilket möjliggör kompatibilitet med både 5V och 3,3V signalnivåer för enkel integration i blandade spänningssystem.

Programmerbar svänghastighet och utgångar med öppen dränering: Du kan styra signalkanthastigheter för EMI-reduktion och välja utgångar med öppen dränering för trådbundna och logik eller nivåskiftning.

Sex global utgångsaktiveringssignaler: Dessa globala styrsignaler möjliggör möjliggörande eller inaktiverande utgångar över flera I/O -banker för effektiv signalhantering.

Konfigurerbara flip-flops i makroceller: Varje macrocell innehåller en flip-flop som stöder förinställning, klar, klocka-aktivering och individuell kontroll, vilket ger förbättrad flexibilitet för sekventiell logikdesign.

Lågeffektläge: Enheten innehåller en kraftbesparande funktion som kan minska makrocellens strömförbrukning med över 50%, vilket är fördelaktigt för energieffektiva applikationer.

JTAG gränsskanningsteststöd : Enheter med 128 eller fler makroceller, som den här, inkluderar fullständiga gränsscanningstestfunktioner för effektiv diagnostik på kortnivå och validering.

Säkerhetsbit för designskydd: En programmerbar säkerhetsbit säkerställer att den interna designen inte kan läsas eller kopieras, vilket skyddar immateriell egendom.

PCI-kompatibel I/O: I/O-strukturen är utformad för att uppfylla PCI-elektriska krav, vilket möjliggör direkt gränssnitt med PCI-baserade system.

Driftstemperaturområde 0 ° C till 70 ° C: Standardtemperaturområdet för kommersiell klass gör denna enhet lämplig för de flesta inomhus- och kontrollerade miljöapplikationer.

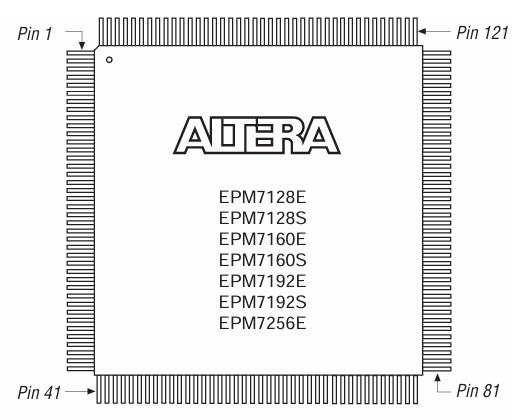

EPM7192SQC160-15 PINOUT DIAGRAM

Detta diagram visar PIN-layouten för EPM7192SQC160-15 och liknande Altera Max 7000S-enheter.Chipet har 160 stift arrangerade runt alla fyra sidor i ett fyrkantigt QFP -paket.Stift 1 börjar vid det övre vänstra hörnet och siffrorna går moturs runt chipet.Varje sida har 40 stift.Den lilla pricken vid de övre vänstra markerar stift 1, vilket hjälper till med korrekt placering.Chipnamnet i mitten visar att det är kompatibelt med andra modeller i samma familj.Denna layout ger många I/O -anslutningar och är användbar för komplexa logikdesign.

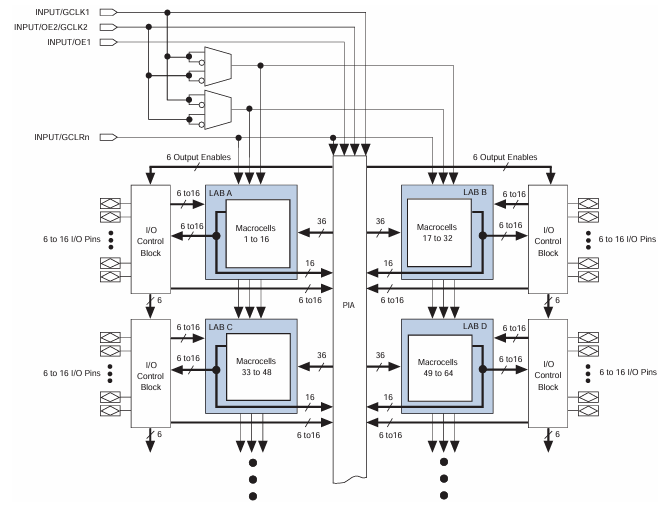

Max 7000s blockschema

Detta blockdiagram visar den interna strukturen för Max 7000S CPLD, inklusive EPM7192SQC160-15.Chipet är uppdelat i fyra huvudsektioner som kallas logik arrayblock (labb A till D).Varje laboratorium har 16 makroceller, som är små logikenheter som används för att bygga digitala kretsar.Tillsammans hanterar dessa labb komplexa logiska operationer.

I mitten är den programmerbara interconnect -arrayen (PIA), som ansluter alla labb och låter dem dela data.Varje labb skickar och tar emot signaler genom 36 kanaler, vilket ger flexibel routing mellan logikblock.Runt kanterna finns I/O -kontrollblock som länkar 6 till 16 I/O -stift till varje labb, vilket gör att enheten kan ansluta till andra delar av ett system.

Överst visas globala styrsignaler som klockor och utgångsaktivering.Dessa signaler hjälper till att hantera hur data rör sig inuti chipet och när utgångarna är aktiva.Sammantaget visar diagrammet hur EPM7192SQC160-15 organiserar sin logik och anslutningar för att stödja anpassade digitala mönster.

EPM7192SQC160-15 Specifikationer

|

Typ |

Parameter |

|

Tillverkare |

Alta |

|

Serie |

Max® 7000s |

|

Förpackning |

Bricka |

|

Delstatus |

Föråldrad |

|

Programmerbar typ |

I systemprogrammerbar |

|

Fördröjningstid TPD (1) Max |

15 ns |

|

Spänningsförsörjning - intern |

4.75V ~ 5.25V |

|

Antal logikelement/block |

12 |

|

Antal makroceller |

192 |

|

Antal grindar |

3750 |

|

Antal I/O |

124 |

|

Driftstemperatur |

0 ° C ~ 70 ° C (TA) |

|

Monteringstyp |

Ytfäste |

|

Förpackning / fodral |

160-bqfp |

|

Leverantörspaket |

160-PQFP (28x28) |

|

Basproduktnummer |

EPM7192 |

EPM7192SQC160-15 Applikationer

Inbäddat systemlimlogik

EPM7192SQC160-15 är idealisk för att överbrygga olika digitala enheter i inbäddade system.Det kan användas för att hantera kommunikation mellan mikrokontroller, minneschips och I/O -enheter genom att hantera adressavkodning, busskontroll och timingjusteringar utan att behöva diskreta logik ICS.

Statliga maskiner och kontrolllogik

Med sina 192 makroceller är chipet väl lämpat för att implementera anpassade tillståndsmaskiner och kontrolllogik.Det används vanligtvis i automatiseringsuppgifter, motorstyrenheter och tidsbaserade kontrollsystem som kräver pålitliga och repeterbara tillståndsövergångar.

Kommunikationsprotokollgränssnitt

Denna CPLD kan programmeras för att skapa eller översätta kommunikationsprotokoll som UART, SPI, I²C eller anpassade serieformat.Det tillåter enkel konfiguration och modifiering utan att ändra hårdvara, vilket gör det värdefullt för kommunikationsgränssnitt.

Förbehandling av digital signal

Tack vare sin snabba logikhastighet och låga förökningsfördröjning kan den hantera enkla signalbehandlingsuppgifter som filtrering, multiplexering eller kantdetektering innan signaler når huvudprocessorn eller DSP -chipet.

Gränssnittsöversättning och nivåskiftning

Dess multivolt I/O -kapacitet stöder både 3.3V- och 5V -signaler.Detta gör det lämpligt för konstruktioner som inkluderar komponenter som arbetar vid olika spänningsnivåer, vilket möjliggör säker och effektiv spänningsöversättning.

Snabb prototyper och uppdateringar i systemet

Du kan använda detta chip i system som kan kräva ofta logiska uppdateringar.Dess EEPROM-baserade struktur och JTAG-programmeringsgränssnitt gör det möjligt att omprogrammera logiken även efter att styrelsen har monterats.

Test och diagnostik på styrelsenivå

Med gränsskanningsstöd via JTAG testar den anslutningarna mellan chips på en PCB utan att behöva sonder.Detta är användbart under tillverkning och diagnostik i fältet för att upptäcka löd- eller routingproblem.

EPM7192SQC160-15 Liknande delar

• EPM7192EQC160-20 (Altera)

Den här enheten kommer från samma Max 7000-serie och erbjuder samma logikresurser, 192 macroceller och 124 I/O-stift i ett 160-stifts PQFP-paket.Den arbetar med en långsammare hastighetskvalitet på –20, vilket innebär att den har längre förseningar i förökningen (~ 20 ns), men det uppfyller fortfarande behoven hos icke-tidskritiska mönster.Det är ett lämpligt alternativ för applikationer där logikdensiteten är viktig, men ultrasnabb timing är inte en prioritering, vilket gör det idealiskt för kostnadskänsliga projekt som fortfarande behöver funktionell ekvivalens.

• EPM7192SQI160-10N (Altera)

Denna del är också logikkompatibel med EPM7192SQC160-15, och erbjuder samma antal makroceller och I/OS.Den använder emellertid en –10 hastighetsklass, som stöder snabbare drift med förbättrad tidpunkt (10 ns fördröjning för förökning).Det stöder också ett utökat temperaturintervall från –40 ° C till +85 ° C, vilket gör det till ett utmärkt ersättning för industriella eller utomhusapplikationer.Detta gör det idealiskt när högre hastighet och miljömässiga motståndskraft krävs.

• EPM7192SQC160-7 (Intel)

Som en direkt speed-up-variant av EPM7192SQC160-15, levererar –7-versionen den snabbaste prestanda i familjen, med förseningar i förökningen ner till 7,5 ns.Den upprätthåller samma stiftkonfiguration, kraftspecifikationer och logikdensitet, och erbjuder en drop-in-ersättning för dem som söker bättre hastighet utan att ändra brädets layout eller spänningskrav.Detta gör det till det bästa valet för tidskritiska mönster som behöver snabbare signalrespons medan du stannar inom samma designavtryck.

EPM7192SQC160-15 Programmeringssteg

1. Ange ISP -läge

Det första steget är att flytta enheten till ISP (in-system-programmering) -läge.Detta görs genom JTAG -gränssnittet.En gång i ISP-läge placeras alla I/O-stift på enheten i ett säkert tri-state-läge för att förhindra oavsiktlig logikstörning under programmering.Denna initialisering tar vanligtvis cirka 1 millisekund.

2. Kontrollera enhets -ID

Ett unikt kisel -ID är inbäddat i enheten för att verifiera att det är rätt modell innan programmeringen börjar.Systemet förskjuts i en läsinstruktion och hämtar ID via TDO (Test Data Out).Denna kontroll säkerställer att programmeringsverktyget är anslutet till höger CPLD och undviker misstag som att skriva över en annan del.

3. Bulkrad

En bulkrader rensar alla tidigare lagrade data i EEPROM -minnet för CPLD.Detta förbereder chipet för att få en ny konfiguration.Raderingskommandot initierar en puls som vanligtvis varar runt 100 millisekunder, vilket säkerställer att alla programmerbara celler återställs.

4. Program EEPROM

Nya konfigurationsdata laddas in i enheten genom att växla adress och databitar genom JTAG -porten.Varje minnescell är skriven en efter en, med en programmeringspuls som appliceras efter varje framgångsrik skrivcykel.Denna process definierar den logiska strukturen som CPLD kommer att använda när den drivs.

5. Verifiera EEPROM

Efter programmering utför enheten ett verifieringssteg.Detta innebär att läsa tillbaka varje programmerad minnesplats och jämföra utgångsvärdena mot de avsedda uppgifterna.Om verifieringen misslyckas måste processen upprepas.Detta steg garanterar att konfigurationen har skrivits framgångsrikt.

6. EXIT ISP -läge

När verifieringen är klar utfärdas ett slutkommando för att lämna ISP -läge.Enheten återaktiverar sina I/O -stift och återupptar normal drift.Denna övergång tar också cirka 1 millisekund och slutför programmeringscykeln i systemet.

EPM7192SQC160-15 Förpackningsdimensioner

• Kroppsstorlek: 28mm × 28mm

• Pakethöjd: 3,4 mm

• Stifthöjd: 0,65 mm

EPM7192SQC160-15 Tillverkare

EPM7192SQC160-15 tillverkades ursprungligen av Anläggningsföretag, ett företag som är känt för sina avancerade programmerbara logikenheter.2015 förvärvades altera av Intel Corporationoch enheten är nu en del av Intels programmerbara lösningsgrupp under Max 7000S CPLD -familjen.Intel fortsätter att stödja Legacy Altera-produkter, även om EPM7192SQC160-15 nu klassificeras som föråldrad i de flesta officiella kataloger.Trots sin avbrutna status säkerställer Intels historiska rykte för tillförlitlighet och Alteras arv i högpresterande logiklösningar fortsatt efterfrågan och tillgängligheten genom sekundära distributörer.

Slutsats

EPM7192SQC160-15 är ett användbart och flexibelt chip för hantering av digitala kontrolluppgifter i många elektroniska system.Det erbjuder tillräckligt med logikkraft för jobb som att bygga anpassade tillståndsmaskiner, hantera signaler och ansluta olika enheter.Den stöder olika spänningsnivåer, fungerar med snabba hastigheter och kan enkelt uppdateras via JTAG.Dess interna design möjliggör smidig signalflöde och enkla logikförändringar.Även om det nu avbryts är det fortfarande ett bra alternativ för gamla eller pågående projekt och kan ersättas med liknande chips som erbjuder snabbare eller bredare temperaturstöd.

Datablad pdf

EPM7192SQC160-15 Datablad:

Om oss

ALLELCO LIMITED

Läs mer

Snabb förfrågan

Skicka en förfrågan, vi svarar omedelbart.

Vanliga frågor [FAQ]

1. Kan jag programmera EPM7192SQC160-15 utan att ta bort det från kretskortet?

Ja, chipet stöder programmering i systemet (ISP) via JTAG-gränssnittet, så att du kan programmera eller omprogrammera det direkt medan det är lödt på PCB, vilket förenklar designuppdateringar och minskar omarbetningen.

2. Vilken programmeringsprogramvara ska jag använda för EPM7192SQC160-15?

Du kan använda Alteras Quartus II-programvara (äldre versioner) för att skapa logikdesign, sammanställa koden och hantera den JTAG-baserade programmeringsprocessen.Quartus II stöder Max 7000S-enheter som EPM7192SQC160-15.

3. Kräver EPM7192SQC160-15 externt minne för drift?

Nej, det har internt EEPROM-baserat konfigurationsminne.All logikkonfiguration lagras inuti chipet, så inget externt minne behövs för att lagra logiktillstånd eller startsekvenser.

4. Vad gör EPM7192SQC160-15 lämplig för industriellt bruk?

Dess robusta 5V-operation, multivolt I/O-kompatibilitet, snabb logikbehandling och EEPROM-baserat icke-flyktigt minne gör det tillförlitligt för industrisystem som kräver stabila och hållbara digitala logikfunktioner.

5. Hur hanterar EPM7192SQC160-15 blandade spänningssystem?

Tack vare sitt multivolt I/O-stöd kan enheten gränssnitt med både 3,3V och 5V logiknivåer, vilket gör den idealisk för blandade signalsystem och gränssnitt med moderna lågspänningskomponenter.

Varför välja EPF10K100EFC484-3 för ditt projekt

på 2025/06/13

Vad är en SPST -switch och hur fungerar det?

på 2025/06/12

Populära inlägg

-

Komplexa instruktionsuppsättningsdatorer: Hur de ändrade datoranvändning?

på 8000/04/18 147770

-

USB-C-pinout och funktioner

på 2000/04/18 111999

-

Använda Xilinx Unified Simulation Primitives: En omfattande guide till FPGA -design och simulering

på 1600/04/18 111351

-

Strömförsörjningsspänningar i elektronik: Betydelsen av VCC, VDD, VEE, VSS och GND

på 0400/04/18 83767

-

RJ45 -anslutningsguide: Pinout, ledningar, kabeltyper och användningar

på 1970/01/1 79558

-

Den ultimata guiden för trådfärgkoder i moderna elektriska system

Hur våra elektriska system använder färger är inte bara för utseende.Varje trådfärg indikerar nu en specifik funktion, vilket gör det lättare att identifiera och hantera elektriska komponenter korr...på 1970/01/1 66957

-

Purge Valve Guide: Funktion, symtom, testning och ersättning för optimal motorprestanda

Purge -ventilen är en viktig del av bilens system som hjälper till att hålla luften ren genom att hantera bränsleångor innan de kan fly in i atmosfären.Detta hjälper inte bara miljön genom att mins...på 1970/01/1 63098

-

Kvalitet (Q) Faktor: Ekvationer och applikationer

Kvalitetsfaktorn, eller 'Q', är viktig när man kontrollerar hur väl induktorer och resonatorer arbetar i elektroniska system som använder radiofrekvenser (RF).'Q' mäter hur väl en krets minimerar e...på 1970/01/1 63039

-

Uppnå toppprestanda med den maximala kraftöverföringssatsen

Den maximala kraftöverföringssatsen förklarar hur energi från en källa, till exempel ett batteri eller generator, flyter till en ansluten belastning.Det visar det exakta tillståndet där lasten får ...på 1970/01/1 54095

-

A23 -batterispecifikationer och kompatibilitet

A23-batteriet är ett litet, cylinderformat batteri med högspänning.Även kallad 23A, 23AE eller MN21, den körs vid 12 volt och mycket högre än AA- eller AAA -batterier.Dess speciella design...på 1970/01/1 52179