EPM7256AETC144-10N CPLD: Datablad, specifikationer, applikationer och programmeringsguide

EPM7256AETC144-10N är en programmerbar logikenhet (CPLD) från Intels Max® 7000A-serie.Detta chip är utformat för snabb prestanda, som körs upp till 172,4 MHz med en fördröjning på 10 ns.Den här guiden förklarar allt om denna CPLD, inklusive dess funktioner, specifikationer, användningar, hur man programmerar den och dess stiftlayout.Om du behöver ett pålitligt, programmerbart chip för digitala kretsar, hjälper den här artikeln dig att förstå hur den fungerar.Katalog

EPM7256AETC144-10N Beskrivning

De EPM7256AETC144-10N är en högpresterande CPLD från Intels Max® 7000A-serie, skräddarsydd för att kräva logikintegrationsuppgifter.Den här enheten har 256 makroceller och cirka 5 000 användbara grindar, vilket underlättar betydande designflexibilitet och användbarhet i komplexa digitala miljöer.Den arbetar med en maximal frekvens på 172,4 MHz med en förökningsfördröjning på endast 5,5 ns, den är konstruerad för snabb drift.EPM7256AETC1444-10N stöder robusta logikdesignkrav (TQFP), designad med en 3,3V driftspänning och förpackas i en kompakt 144-stifts tunn fyrhjuling.EPM7256AETC144-10N använder EEPROM-baserade icke-flyktiga konfigurationsminne, vilket möjliggör permanent lagring av programmeringsdata.Denna funktion, i kombination med programmerbarhet i systemet via JTAG-gränssnittet, ger lättare uppdateringar och fältprogrammering, vilket förbättrar långvarig användbarhet utan behov av fysisk rekonfiguration eller ersättning.

Säkra dina projekt med pålitlig, fältteknologi genom att placera din bulkorder för EPM7256AETC144-10N med oss idag och se till att du har en solid CPLD-lösning.

EPM7256AETC144-10N CAD-modeller

EPM7256AETC144-10N Symbol

EPM7256AETC144-10N FOTPRINT

EPM7256AETC144-10N 3D-modell

EPM7256AETC144-10N Funktioner

Makroceller:Den här enheten är utrustad med 256 makroceller.Makroceller är de konfigurerbara logikkomponenterna som gör att CPLD kan utföra olika logikfunktioner.

Användbara grindar:Det ger cirka 5 000 användbara grindar.Detta hänvisar till motsvarande mängd grundläggande logikgrindar (som och, eller, inte) som kan konfigureras i enheten.

I/O -stift:CPLD har 120 ingångs-/utgångsstift, som möjliggör omfattande gränssnitt med andra delar av en användares elektroniska design.

Förökningsfördröjning (TPD):Den maximala förökningsförseningen är 10 nanosekunder, vilket bestämmer hur snabbt CPLD kan bearbeta insignaler och producera utgångar.

Driftsfrekvens:Den kan fungera vid frekvenser upp till 95,2 MHz, som definierar hastigheten med vilken enheten kan utföra logikoperationerna.

Matningsspänning:Enheten arbetar med en matningsspänning på 3,3V, i linje med vanliga lågspänningsiditala logiknivåer.

Paket:Den finns i en 144-stifts tunn quad-platt-förpackning (TQFP), en kompakt pakettyp som är gynnsam för att minimera utrymmet som krävs på tryckta kretskort.

Driftstemperaturområde:Drifttemperaturområdet är från 0 ° C till 70 ° C, vilket säkerställer tillförlitlig prestanda över ett brett spektrum av miljöförhållanden.

Programmerbarhet i systemet:CPLD stöder programmerbarhet i systemet via en IEEE STD.1149.1 Joint Test Action Group (JTAG) -gränssnitt, vilket möjliggör programmering och omprogrammering av logikenheten inom den slutliga hårdvarukonfigurationen.

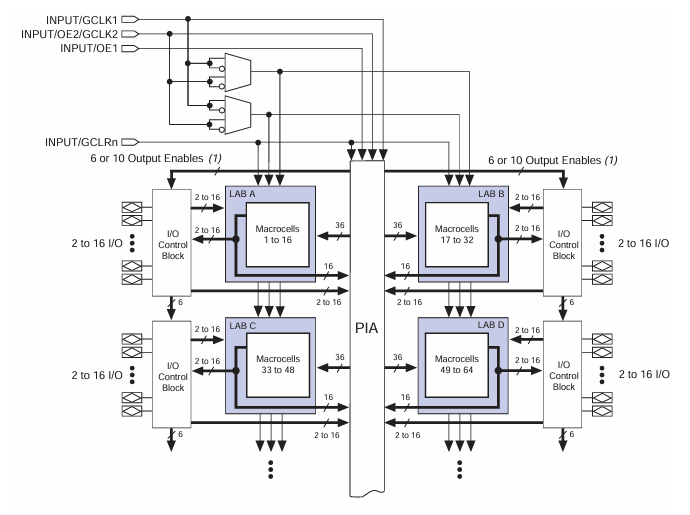

EPM7256AETC144-10N BLOCK DIAGRAM

De EPM7256AETC144-10N är en Komplex programmerbar logikenhet (CPLD) med fyra Logic Array Blocks (Labs) , var och en innehåller 16 makroceller, totalt 64 makroceller.Dessa makroceller hanterar både kombinations- och sekventiell logik, vilket gör enheten flexibel för olika digitala logiska applikationer.I mitten av CPLD är Programmerbar samtrafik Array (PIA), som ansluter alla laboratorier och säkerställer effektiv signalrutning.Varje labb kommunicerar med PIA med 36 sammankopplingslinjer, vilket gör att signaler kan delas och bearbetas effektivt.Enheten har I/O -kontrollblock på varje sida, som stöder 2 till 16 I/O -stift per laboratorium.Dessa block hjälper till att hantera ingångs- och utgångsfunktioner och ansluta CPLD till externa kretsar.Kontrollsignaler som Global Clocks (GCLK1, GCLK2), utgångsaktiveringar (OE1) och Global Reset (GCLRN) hjälper till att synkronisera logikoperationer över enheten.Dessutom hanterar logiska grindar klocka och återställer signaler, vilket säkerställer smidig drift.Denna CPLD är utformad för höghastighetslogikbehandling, erbjuder programmerbarhet, effektiv signalruttning och pålitlig I/O-kontroll, vilket gör den lämplig för inbäddade system, kommunikation och industriell automatisering.

EPM7256AETC144-10N Specifikationer

|

Typ |

Parameter |

|

Tillverkare |

Altera/intel |

|

Serie |

MAX® 7000A |

|

Förpackning |

Bricka |

|

Delstatus |

Föråldrad |

|

Programmerbar typ |

I systemprogrammerbar |

|

Fördröjningstid TPD (1) Max |

10 ns |

|

Spänningsförsörjning - intern |

3V ~ 3,6V |

|

Antal logikelement/block |

16 |

|

Antal makroceller |

256 |

|

Antal grindar |

5000 |

|

Antal I/O |

120 |

|

Driftstemperatur |

0 ° C ~ 70 ° C (TA) |

|

Monteringstyp |

Ytfäste |

|

Förpackning / fodral |

144-LQFP |

|

Leverantörspaket |

144-TQFP (20x20) |

|

Basproduktnummer |

EPM7256 |

EPM7256AETC144-10N-applikationer

Konstgjorda intelligens

Denna CPLD används i AI -hårdvaruacceleratorer för att hantera komplexa beräkningar som krävs för bearbetning av AI -algoritmer effektivt, vilket förbättrar både hastighet och tillförlitlighet i AI -applikationer.

5G -teknik

På området 5G-kommunikation är EPM7256AETC144-10N bäst för signalbehandling och hantering av kommunikationsprotokoll.Dess höghastighetslogikoperationer underlättar den snabba behandlingen som behövs i nästa generation av trådlösa system.

Molnberäkning

Inom datacenter förbättrar denna enhet bearbetningsfunktioner och fungerar som komponent för att hantera höga volymer av data och komplexa beräkningar, vilket stödjer infrastrukturen för molntjänster.

Konsumentelektronik

CPLD hittar applikationer inom konsumentelektronik som tv -apparater och spelkonsoler, där den utför anpassade logikfunktioner som förbättrar enhetsfunktionerna och upplevelsen.

Trådlös teknik

Det används i trådlösa kommunikationsenheter för att modulera och demodulera signaler, vilket säkerställer effektiv och effektiv kommunikation i enheter som routrar och mobilmodem.

Industriell kontroll

Den här enheten är integrerad i automatiseringssystem i industriella miljöer, där den styr maskiner och hanterar processer, vilket bidrar till ökad produktivitet och säkerhet.

Internet of Things (IoT)

I IoT-enheter hanterar EPM7256AETC144-10N databehandling och kommunikationsuppgifter, bra för den sömlösa driften av anslutna enheter i smarta hem och industrier.

Medicinsk utrustning

CPLD tillämpas i medicintekniska produkter för uppgifter som datainsamling och signalbehandling, spelar en roll i tillförlitligheten och effektiviteten i medicinsk diagnostik och behandlingsutrustning.

EPM7256AETC144-10N Liknande delar

EPM7256AETC144-10N Fördelar

Hög logisk täthet

Den här enheten packar 256 makroceller och cirka 5 000 användbara grindar, vilket möjliggör implementering av komplexa logikkretsar inom ett enda chip.Denna höga logikdensitet underlättar mer integrerade och kompakta konstruktioner, vilket minskar det övergripande komponentantalet och förenklande styrlayouter.

Programmerbarhet i systemet (ISP)

Med programmerbarhet i systemet via en IEEE STD.1149.1 JTAG-gränssnitt, EPM7256AETC144-10N möjliggör enkel programmering och omprogrammering direkt i kretsen.Denna kapacitet är ovärderlig för snabb prototypning och iterativa designprocesser, vilket gör det möjligt för justeringar utan att behöva ersätta chipet.

Snabb utbredningsfördröjning

Med en maximal förökningsfördröjning på bara 10 ns säkerställer denna CPLD snabbbehandling av ingångar och utgångar för applikationer som kräver höghastighetsdatahantering och snabba svar, såsom videobearbetning och högfrekventa handelssystem.

Låg effektförbrukning

EPM7256AETC144-10N fungerar på en 3,3V matningsspänning är optimerad för energieffektivitet.Denna låga kraftförbrukning är fördelaktig i bärbara och batteridrivna enheter, där krafthantering är bra för att förlänga driftslivet.

Omfattande I/O -kapacitet

Enheten är utrustad med 120 I/O -stift, vilket ger omfattande anslutningsalternativ.Detta möjliggör flexibel gränssnitt med ett brett utbud av kringutrustning och andra systemkomponenter, vilket gör det mycket anpassningsbart till komplexa miljöer med flera enheter.

Icke-flyktig konfigurationslagring

Tack vare sitt EEPROM-baserade minne behåller CPLD sina konfigurationsinställningar även efter att strömmen har stängts av, vilket säkerställer att enhetens funktionalitet förblir konsekvent över effektcykler.Denna funktion behövs för applikationer som kräver pålitlig, långsiktig prestanda utan behov av ofta rekonfiguration.

EPM7256AETC144-10N Programmeringssteg

Programmering av EPM7256AETC144-10N-enheten involverar en sexstegs in-system-programmeringsprocess (ISP):

1. ENTER ISP: Detta steg ser till att ingångs- och utgångsdelarna på enheten växlar från normal användning till programmeringsläge smidigt.Det tar cirka 1 millisekund.

2. Kontrollera ID: Innan du startar programmering kontrollerar enheten sitt eget ID.Detta steg är väldigt snabbt.

3. Bulk Radera: Detta rensar alla tidigare data från enheten.Det gör detta genom att få ett kommando för att radera allt och sedan vänta på 100 millisekunder för att se till att allt raderas.

4. Program: Det är här de nya uppgifterna läggs in i enheten.För varje data skickas den till rätt adress i enheten, och sedan ser en speciell puls till att den lagras korrekt.

5. Verifiera: Efter programmering kontrollerar enheten om all data lagras korrekt genom att läsa den tillbaka och jämföra den med vad den ska vara.

6. EXIT ISP: Detta steg växlar tillbaka enheten från programmeringsläge till normal användningsläge.Det tar också cirka 1 millisekund.

Den totala tiden som behövs för programmering beror på hur länge varje puls varar och hur snabba data kan gå in och ut ur enheten, vilket påverkas av hastigheten på programmeringsklockan och hur mycket data det finns att bearbeta.Olika enheter kan ta olika mängder tid eftersom de har olika mängder minne att programmera.

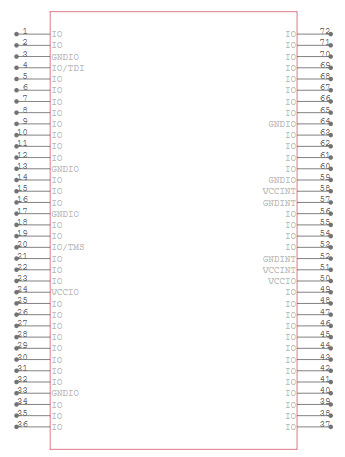

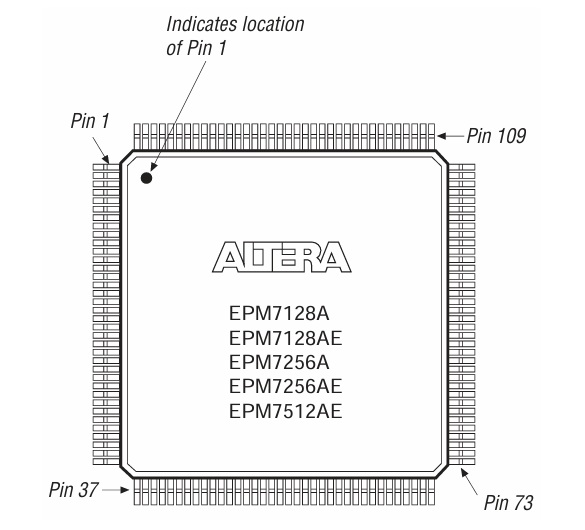

EPM7256AETC144-10N PACKAG PIN-OUT DIAGRAM

Diagrammet visar EPM7256AETC144-10N-paketet och numrering.Detta chip kommer i en TQFP-144 (Thin Quad Flat Package med 144 stift), vilket betyder att det har fina ledningar på alla fyra sidor.Pin 1 -platsen är markerad med en liten prick och numret ökar moturs runt paketet.Nyckelreferensstift som stift 1, stift 37, stift 73 och stift 109 hjälper till med orientering under PCB -montering.Konturdimensionerna definierar chipets fysiska storlek för att säkerställa korrekt PCB -montering.Pinoutarrangemanget möjliggör effektiv signalruttning, vilket gör den lämplig för komplexa logiska tillämpningar.EPM7256AE är en del av Max 7000A CPLD-serien, med 256 macroceller och programmerbarhet i systemet.Suffixet -10N indikerar en 10 ns hastighetsklass och ett blyfritt paket.

EPM7256AETC144-10N Tillverkare

EPM7256AETC144-10N är en komplex programmerbar logikenhet (CPLD) som ursprungligen utvecklats av Altera Corporation, som senare förvärvades av Intel Corporation 2015. Sedan förvärvet blev Intel den officiella tillverkaren av Alteras FPGA- och CPLD -produktlinjer, inklusive Max® 7000A -serien, som den här enheten tillhör.EPM7256AETC144-10N är utformad för högpresterande applikationer med låg effekt, som stöder programmerbarhet i systemet (ISP) via JTAG (IEEE 1149.1).Även om Intel ärvde Alteras CPLD -teknik har den här enheten sedan dess avbrutits och klassificeras nu som föråldrad, vilket innebär att Intel inte längre producerar eller stöder den i aktiv tillverkning.

Slutsats

EPM7256AETC144-10N är en kraftfull och flexibel CPLD som används i AI, 5G, molnberäkning, industrimaskiner, IoT och medicintekniska produkter.Den bearbetar data snabbt, använder liten kraft och möjliggör enkel omprogrammering utan att ta bort dem från kretsen.Det är fortfarande användbart för äldre mönster som behöver programmerbar logik med stabil prestanda.Oavsett om du arbetar med denna CPLD eller letar efter liknande alternativ, förstå dess design, programmering och fördelar kan hjälpa dig att utnyttja den bäst i den digitala applikationer med hög hastighet.

Datablad pdf

EPM7256AETC144-10N Datablad:

Om oss

ALLELCO LIMITED

Läs mer

Snabb förfrågan

Skicka en förfrågan, vi svarar omedelbart.

Vanliga frågor [FAQ]

1. Hur många logikelement eller grindar kan EPM7256AETC144-10N-handtaget?

EPM7256AETC144-10N tillhandahåller 256 macroceller och cirka 5 000 användbara grindar, vilket möjliggör måttligt komplexa logiska implementeringar.

2. Hur programmerar jag EPM7256AETC144-10N, och vilka verktyg behöver jag?

EPM7256AETC144-10N stöder programmerbarhet i systemet (ISP) via JTAG (IEEE 1149.1) -gränssnittet.Du behöver en Altera USB-Blaster eller Intel Quartus Prime-programvara för att skriva konfigurationsdata till chipet.

3. Vilka är skillnaderna mellan EPM7256AETC144-10N och EPM7256AETC144-7?

Den primära skillnaden är hastighet.EPM7256AETC144-10N har en maximal förökningsfördröjning på 10 ns, medan EPM7256AETC144-7 har en snabbare 7 NS-fördröjning för högre hastighetsapplikationer.Båda enheterna delar samma paket, I/O -räkning och makrocellstruktur.

4. Kräver EPM7256AETC144-10N en extern oscillator?

Nej, själva CPLD kräver inte en extern oscillator, men den stöder externa klockingångar.Om din design behöver exakt tidpunkt kan en extern klocksignal användas för att driva sina logiska operationer.

5. Vad gör EPM7256AETC144-10N annorlunda än andra CPLD i Max 7000A-serien?

Denna CPLD sticker ut på grund av dess höghastighetsprestanda (10 ns fördröjning), 256 macroceller och 5 000 användbara grindar, vilket gör det idealiskt för komplexa logikdesign.Det stöder också programmerbarhet i systemet (ISP) via JTAG, till skillnad från vissa äldre modeller.

MPC8245LZU300D -processor: Datablad, funktioner, applikationer och specifikationer

på 2025/03/13

En enkel guide till L1154 -batterier för vardagsbruk

på 2025/03/13

Populära inlägg

-

Komplexa instruktionsuppsättningsdatorer: Hur de ändrade datoranvändning?

på 8000/04/18 147772

-

USB-C-pinout och funktioner

på 2000/04/18 112009

-

Använda Xilinx Unified Simulation Primitives: En omfattande guide till FPGA -design och simulering

på 1600/04/18 111351

-

Strömförsörjningsspänningar i elektronik: Betydelsen av VCC, VDD, VEE, VSS och GND

på 0400/04/18 83768

-

RJ45 -anslutningsguide: Pinout, ledningar, kabeltyper och användningar

på 1970/01/1 79565

-

Den ultimata guiden för trådfärgkoder i moderna elektriska system

Hur våra elektriska system använder färger är inte bara för utseende.Varje trådfärg indikerar nu en specifik funktion, vilket gör det lättare att identifiera och hantera elektriska komponenter korr...på 1970/01/1 66960

-

Purge Valve Guide: Funktion, symtom, testning och ersättning för optimal motorprestanda

Purge -ventilen är en viktig del av bilens system som hjälper till att hålla luften ren genom att hantera bränsleångor innan de kan fly in i atmosfären.Detta hjälper inte bara miljön genom att mins...på 1970/01/1 63100

-

Kvalitet (Q) Faktor: Ekvationer och applikationer

Kvalitetsfaktorn, eller 'Q', är viktig när man kontrollerar hur väl induktorer och resonatorer arbetar i elektroniska system som använder radiofrekvenser (RF).'Q' mäter hur väl en krets minimerar e...på 1970/01/1 63040

-

Uppnå toppprestanda med den maximala kraftöverföringssatsen

Den maximala kraftöverföringssatsen förklarar hur energi från en källa, till exempel ett batteri eller generator, flyter till en ansluten belastning.Det visar det exakta tillståndet där lasten får ...på 1970/01/1 54097

-

A23 -batterispecifikationer och kompatibilitet

A23-batteriet är ett litet, cylinderformat batteri med högspänning.Även kallad 23A, 23AE eller MN21, den körs vid 12 volt och mycket högre än AA- eller AAA -batterier.Dess speciella design...på 1970/01/1 52184