LFEC3E-3Q208C FPGA Översikt: Funktioner, applikationer, programmering och specifikationer

I den här artikeln kommer du att lära dig om LFEC3E-3Q208C, en FPGA från Lattice Semiconductor.Du ser vad det är, huvudfunktionerna den erbjuder och varför det är användbart för många mellanslag.Innehållet leder dig också genom sina specifikationer, applikationer och steg-för-steg-programmeringsprocess, tillsammans med dess för-, nackdelar och tillverkarinformation.Katalog

Vad är LFEC3E-3Q208C?

De LFEC3E-3Q208C är en kostnadseffektiv fältprogrammerbar grindarray (FPGA) från Lattice Semiconductor, designad som en del av familjen Latticeec (Economy).Denna familj utvecklades för att leverera programmerbara logiklösningar som balanserar överkomliga priser med tillförlitlig prestanda för mainstream -mönster.Inom Latticeec-hierarkin sitter den i mellanområdet och erbjuder cirka 3 000 logikelement och effektiv kraftanvändning, överbryggar klyftan mellan mindre inträdesenheter och större, mer resursintensiva modeller.Den bredare LATTICEECP/EC-serien betonar lågkostnadsprogrammerbarhet, skalbarhet och flexibilitet i flera enhetsstorlekar, med EC-varianten med fokus på ekonomidriven prestanda.

Letar du efter LFEC3E-3Q208C?Kontakta oss för att kontrollera nuvarande lager, ledtid och prissättning.

LFEC3E-3Q208C-funktioner

• Logikresurser

Enheten integrerar cirka 3 100 logikelement organiserade i 384 block, vilket ger den tillräckligt med kapacitet för mellanklasskonstruktioner.Denna resursbalans gör den lämplig för kontrolllogik, signalbehandling och inbäddade applikationer utan överdrivna kostnader.

• Programmerbar I/O

Med upp till 145 programmerbara ingångs-/utgångsstift stöder det ett brett utbud av anslutningsalternativ.Dessa I/OS är kompatibla med flera standarder som LVCMO, LVTTL, LVDS, PCI och SSTL, vilket möjliggör flexibel systemintegration.

• Inbäddat minne

FPGA inkluderar dedikerade block RAM (EBR) och distribuerade RAM-resurser, vilket ger effektiv lagring på chip.Detta gör det möjligt att implementera databuffring, uppslagstabeller eller små inbäddade minnen direkt inuti enheten.

• Klockstyrelse

Den har upp till fyra integrerade PLL: er som erbjuder frekvensmultiplikation, uppdelning och fasförskjutning.Detta möjliggör exakt tidskontroll och synkronisering för höghastighetsdesign.

• DDR -minnesstöd

Enheten innehåller hårdvarustöd för DDR -gränssnitt, som kan köra DDR400 (200 MHz).Detta gör det praktiskt för mönster som kräver externt höghastighetsminnesåtkomst.

• Krafteffektivitet

FPGA, som arbetar med en 1,2 V -kärntillförsel, minimerar den totala systemkraftsförbrukningen.Dess lågeffektdesign är idealisk för bärbara eller energikänsliga applikationer.

• Systemnivåfunktioner

Inbyggda funktioner som IEEE 1149.1 Gränsskanning, logikanalys on-chip (ISPTracy) och ett SPI-startblashgränssnitt förenklar testning och felsökning.Dessa funktioner minskar utvecklingstiden och förbättrar designens tillförlitlighet.

• Utvecklingsstöd

Med stöd av ISLEVER-designsviten drar enheten fördelar av automatiserad syntes, plats-och-väg och verifieringsverktyg.Du kan också använda ISPLEVERCORE IP-block för att påskynda vanliga funktioner och förkorta tid till marknad.

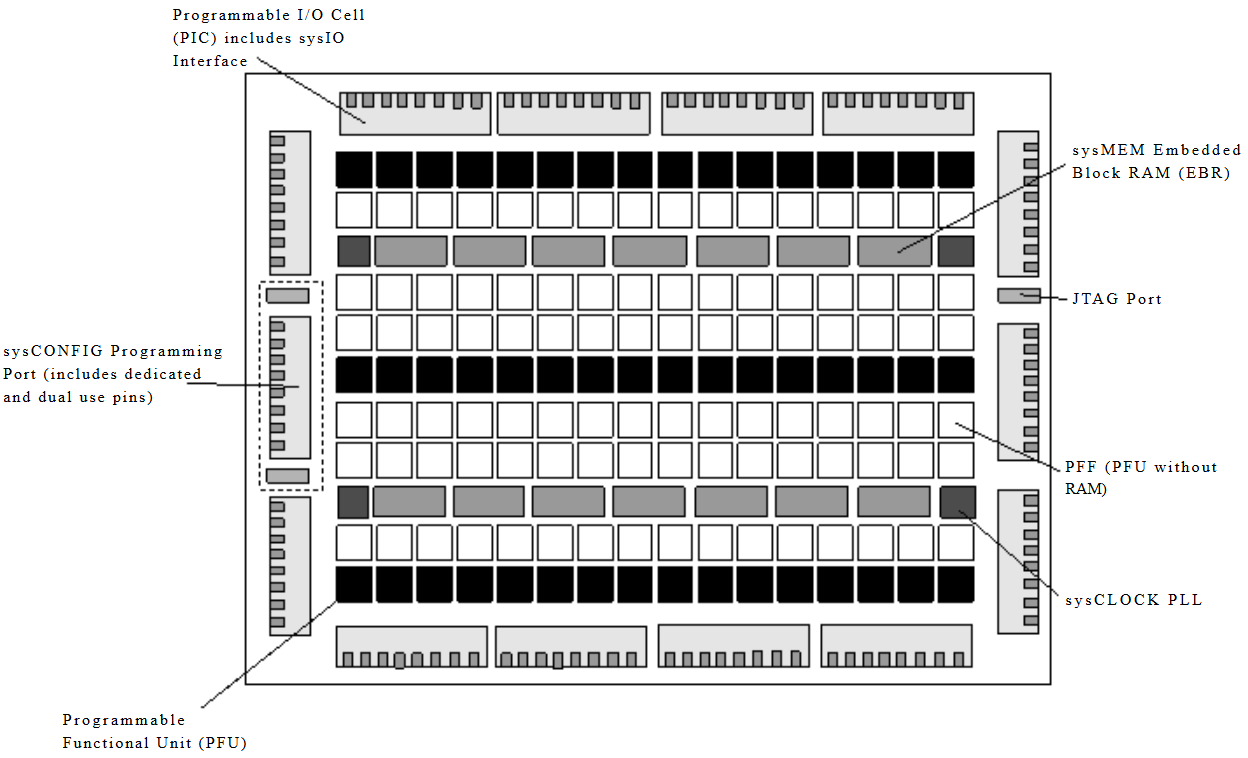

LATTICEECP/EC Family Block Diagram

Blockdiagrammet för LATTICEECP/EC-familjen (inklusive LFEC3E-3Q208C) visar hur FPGA är byggd och hur dess delar fungerar tillsammans.De programmerbara I/O -cellerna (PIC) placeras runt kanterna för att ansluta chipet med externa enheter och stödja många signalstandarder.Inuti hanterar de programmerbara funktionella enheterna (PFUS) logikoperationer, med några parade till inbäddade block RAM (EBR) för att lagra data och andra endast fokuserade på logik.Sysclock PLL: er hanterar klocksignaler så att designen kan köras med rätt hastighet och timing.Sysconfig -porten och JTAG -porten låter dig programmera, testa och felsöka FPGA enkelt.Denna layout ger LFEC3E-3Q208C flexibilitet, tillförlitlig prestanda och enkel integration i kostnadskänsliga mönster.

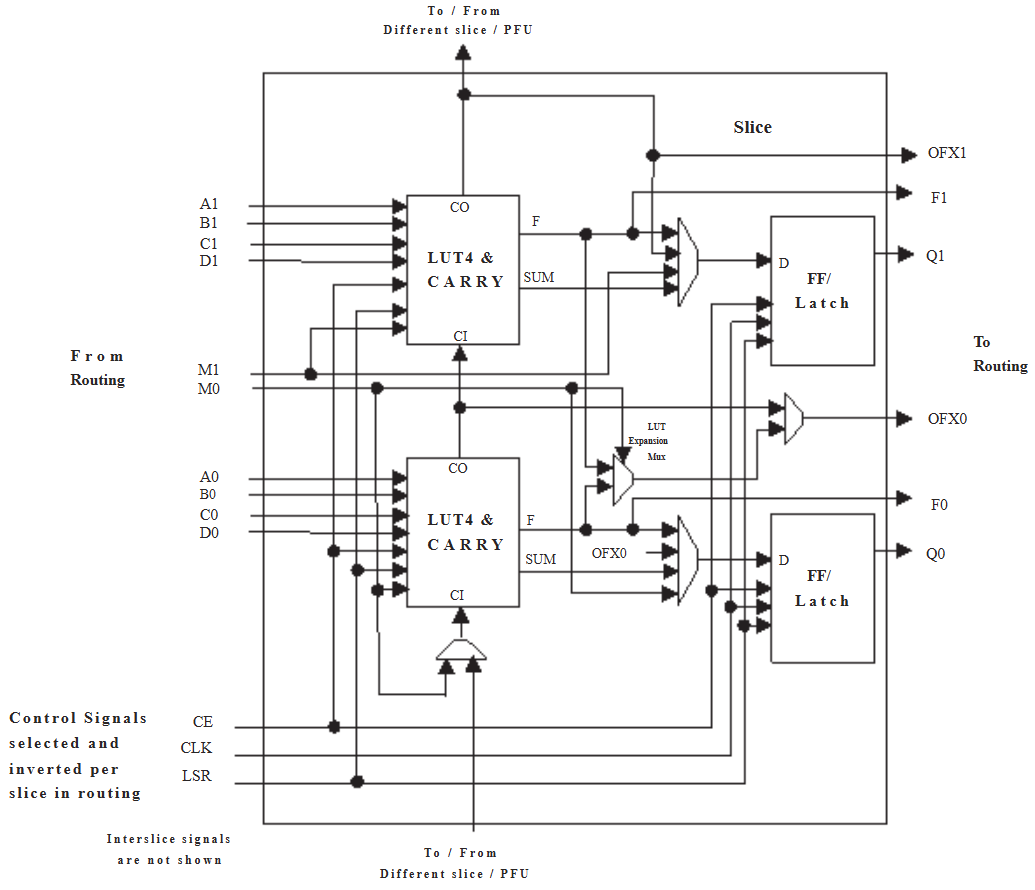

LatticeECP/EC -skivdiagram

Skivan i LatticeECP/EC-familjen, som i LFEC3E-3Q208C, är Core Logic-enheten som kombinerar LUT4 & Carry-block för att utföra logik och aritmetiska operationer.Varje skiva innehåller också flip-flops/spärrar för att lagra data och möjliggöra sekventiell logik, med multiplexerare för att dirigera signaler flexibelt antingen genom register eller direkt.Denna struktur är viktig eftersom den ger FPGA -hastigheten, flexibiliteten och effektiviteten för att hantera både enkla och komplexa digitala mönster.Följande tabell sammanfattar skivsignalbeskrivningarna, inklusive deras funktioner, typer, signalnamn och syften.

|

Fungera |

Typ |

Signalnamn |

Beskrivning |

|

Input |

Signal |

A0, B0, C0, D0 |

Ingångar till LUT4 |

|

Input |

Signal |

A1, B1, C1, D1 |

Ingångar till LUT4 |

|

Input |

Mångsidig |

M0 |

Mångsidig ingång |

|

Input |

Mångsidig |

M1 |

Mångsidig ingång |

|

Input |

Styrsignal |

Ces |

Klocka Aktivera |

|

Input |

Styrsignal |

Lsr |

Lokal uppsättning/återställning |

|

Input |

Styrsignal |

Klk |

Systemklocka |

|

Input |

Inter-pfu-signal |

Fcin |

Snabb bär i¹ |

|

Produktion |

Datasignaler |

F0, F1 |

LUT4 utgångsregister bypass -signaler |

|

Produktion |

Datasignaler |

Q0, Q1 |

Registerutgångar |

|

Produktion |

Datasignaler |

Ofx0 |

Utgång från en LUT5 MUX |

|

Produktion |

Datasignaler |

Ofx1 |

Utgång från en LUT6, LUT7, LUT8 2 MUX beroende på skivan |

|

Produktion |

Inter-pfu-signal |

Fco |

För den högra PFU är den snabba bärkedjan utgången |

LFEC3E-3Q208C-specifikationer

|

Typ |

Parameter |

|

Tillverkare |

Gitterhalvledare |

|

Spänning - försörjning |

1.14V ~ 1.26V |

|

Totala RAM -bitar |

56,320 |

|

Leverantörspaket |

208-PQFP (28x28) |

|

Serie |

Ec |

|

Förpackning / fodral |

208-bfqfp |

|

Paket |

Bricka |

|

Driftstemperatur |

0 ° C ~ 85 ° C (TJ) |

|

Antal logikelement/celler |

3 100 |

|

Antal I/O |

145 |

|

Monteringstyp |

Ytfäste |

|

Basproduktnummer |

Lfec3 |

LFEC3E-3Q208C-applikationer

1. Inbäddade kontrollsystem

LFEC3E-3Q208C är väl lämpad för inbäddade styrenheter i enheter, industriell automatisering och IoT-gateways.Dess måttliga logikdensitet och lågkostnadsdesign gör det möjligt att ersätta fastfunktionslogik med programmerbar flexibilitet.Detta gör det lättare att uppgradera system eller anpassa sig till utvecklande standarder utan omarbetning av hårdvara.

2. DDR -minne gränssnitt

Med inbyggt stöd för DDR400-minne kan enheten hantera databuffring, loggning eller tillfällig lagring i applikationer.Denna funktion är användbar i system där extern minneshastighet är viktig men full avancerad FPGA-prestanda krävs inte.Många drar nytta av en balans mellan hastighet, kostnad och minneseffektivitet.

3. I/O -överbryggning och protokollomvandling

Tack vare sitt breda stöd för I/O -standarder som LVCMOS, LVTTL, LVDS, PCI och SSTL är FPGA effektiv för att överbrygga olika digitala gränssnitt.Det kan konfigureras för att översätta signaler mellan delsystem, vilket gör det värdefullt i blandat teknologi.Denna flexibilitet hjälper till att förlänga livslängden för befintlig hårdvara genom att möjliggöra kompatibilitet med nya komponenter.

4. Industriella och infrastrukturapplikationer

Enheten kan också tjäna i kostnadskänslig industriell och infrastrukturutrustning där tillförlitlighet och måttlig prestanda är tillräcklig.Dess stöd för gränsskanning, felsökning på chip och låg effekt gör det idealiskt för system som kräver effektivitet och enkelt underhåll.Typiska roller inkluderar kontrollenheter, gränssnittsmoduler och övervakningssystem.

LFEC3E-3Q208C Liknande delar

|

Specifikation |

LFEC3E-3Q208C |

LFEC3E-3Q208I |

LFEC3E-3QN208C |

LFEC3E-4Q208C |

LFEC1E-3Q208C

|

LFEC6E-3Q208C

|

|

Logikelement (LUTS) |

~ 3,1K |

~ 3,1K |

~ 3,1K |

~ 3,1K |

~ 1,5K |

~ 6,1K |

|

Logikblock |

384 |

384 |

384 |

384 |

192 |

768 |

|

Inbäddat block RAM (EBR) |

~ 55 kb |

~ 55 kb |

~ 55 kb |

~ 55 kb |

~ 18 kb |

~ 92 kb |

|

Max driftsfrekvens |

~ 340 MHz |

~ 340 MHz |

~ 340 MHz |

~ 340 MHz |

~ 300 MHz |

~ 340 MHz |

|

I/O räknas |

145 |

145 |

145 |

145 |

112 |

145 |

|

Paket |

208-pqfp |

208-pqfp |

208-pqfp |

208-pqfp |

208-pqfp |

208-pqfp |

|

Kärnspänning |

1,2 v |

1,2 v |

1,2 v |

1,2 v |

1,2 v |

1,2 v |

|

Temperaturområde |

0 ° C till +70 ° C |

–40 ° C till +85 ° C |

0 ° C till +70 ° C |

0 ° C till +70 ° C |

0 ° C till +70 ° C |

0 ° C till +70 ° C |

|

Efterlevnad / pakettyp |

Standard |

Industriell |

Lead-Free (QN) |

Variant (Q) |

Standard |

Standard |

|

Ansökan |

Mitten av densitet, allmänt syfte |

Samma som LFEC3E men industriellt bruk |

Samma som LFEC3E men paketkompatibelt |

Samma familj, enkel migration |

Lågdensitetskostnadsalternativ |

Uppgradering av högre densitet |

LFEC3E-3Q208C-programmeringssteg

Innan du börjar programmera LFEC3E-3Q208C är det viktigt att förbereda rätt verktyg och förstå flödet av design till enhetskonfiguration.Varje steg bygger på det föregående, så noggrann uppmärksamhet kommer att säkerställa en smidig programmeringsprocess.

1. Förbered programmeringshårdvara och programvara

Du börjar med att installera Lattice's Diamond Programmer eller ISPVM -system, som är de officiella verktygen för denna FPGA.Ställ sedan in JTAG-programmeringskabeln som HW-USBN-2B och se till att drivrutinerna är korrekt installerade.Detta steg säkerställer att din dator är redo att kommunicera med målenheten utan anslutningsfel.

2. Implementera din design i utvecklingsprogramvara

Skapa sedan ett nytt projekt i Lattice Diamond och välj LFEC3E-3Q208C som din målenhet.Du lägger sedan till dina Verilog- eller VHDL -källfiler, tillämpar PIN -tilldelningar och definierar eventuella tidsbegränsningar.När det är gjort syntetiserar du designen, utför plats-och-väg och genererar slutligen bitströmmen (.bit eller .jed) som kommer att användas för programmering.

3. Ställ in brädet och anslutningarna

Anslut nu JTAG -kabeln till ditt FPGA -kort och se till att markanslutningen är säker innan du fäster signallinjerna.Bekräfta att pull-up- och pull-down-motstånd är korrekt på plats, särskilt på TCK och öppna avdrag.Om ditt kort har ytterligare kontrollstift som Radera eller Ispen måste du konfigurera dem ordentligt för att förhindra oavsiktliga återställningar under programmering.

4. Programmera enheten

Starta programmeringsverktyget med hårdvaran klar och välj din anslutna kabel.Ladda den genererade bitströmfilen och välj lämpligt läge, vanligtvis JTAG, beroende på din installation.Starta programmeringsprocessen och verktyget konfigurerar FPGA medan du verifierar att uppgifterna har skrivits korrekt.

5. Verifiera och felsöka konfigurationen

Efter programmering, kontrollera de gjort eller init -stiften på ditt bräde för att bekräfta att FPGA har konfigurerat framgångsrikt.Använd vid behov ISPTracy Logic Analyzer eller gränsskanningsfunktioner för att testa funktionalitet och validera signalbeteende.Du kan upprepa design- och programmeringscykeln när ändringar krävs, vilket säkerställer att ditt projekt förfinas steg för steg.

LFEC3E-3Q208C Fördelar och nackdelar

Fördelar

• Låg effektförbrukning, lämplig för energikänsliga mönster

• Kostnadseffektivt jämfört med högre FPGA

• Enkel verktygskedja med enklare inlärningskurva

• Fältkonfigurerbar för uppdateringar efter distributionen

• Kompakt paket med god resursbalans

Nackdelar

• Begränsad prestanda jämfört med större FPGA

• Lägre logik- och minneskapacitet än avancerade enheter

• Färre tredjeparts IP-kärnor och ekosystemstöd

• Toolchain saknar avancerade funktioner hos stora leverantörer

• Inte passande för ultrahöghastighetsgränssnitt

LFEC3E-3Q208C förpackningsdimensioner

|

Typ |

Parameter |

|

Pakettyp |

208-PQFP (plastfyrnadsplattpaket) |

|

Kroppsstorlek |

28 mm × 28 mm |

|

Tonhöjd |

0,5 mm |

|

Pakethöjd (max) |

~ 3,4 mm |

|

Ledningsantal |

208 stift |

|

Paketstil |

Gull-Wing Leads (Quad) |

|

Monteringstyp |

Ytfäste |

|

Fallkod |

BFQFP-208 |

|

Leverantörspaket |

Bricka |

LFEC3E-3Q208C tillverkare

LFEC3E-3Q208C tillverkas av Gitter Semiconductor Corporation , ett amerikanskt företag med huvudkontor i Hillsboro, Oregon.Grundades 1983 och är specialiserad på att utveckla lågeffekt, kostnadseffektiva fältprogrammerbara grindarrayer (FPGA) och relaterade lösningar.Företaget fokuserar på att möjliggöra applikationer inom kommunikation, dator, konsumentelektronik, industri- och bilmarknader.Litteret är känt för sin innovation inom energieffektiva programmerbara enheter och har etablerat sig som en nyckelaktör inom FPGA-industrin, särskilt för mönster som kräver kompakta formfaktorer, minskad strömförbrukning och hög tillförlitlighet.

Slutsats

LFEC3E-3Q208C erbjuder en bra blandning av låg kostnad, låg effektanvändning och tillräckligt med logik och minne för mellanklassprojekt.Det stöder många I/O-standarder, har inbyggda RAM och PLL: er och kan arbeta med DDR400-minne, vilket gör det användbart för kontroll-, gränssnitt och industriella uppgifter.Programmering är enkel med gitterverktyg, och extra felsökningsfunktioner hjälper till att testa.Även om den inte kan matcha hastigheten och kapaciteten för större FPGA: er, är det ett pålitligt val för mönster som behöver flexibilitet, effektivitet och prisvärd prestanda.

Datablad pdf

LFEC3E-3Q208C Datablad:

Om oss

ALLELCO LIMITED

Läs mer

Snabb förfrågan

Skicka en förfrågan, vi svarar omedelbart.

Vanliga frågor [FAQ]

1. Stöder LFEC3E-3Q208C höghastighetsgränssnitt som PCIe eller Gigabit Ethernet?

Nej. LFEC3E-3Q208C är utformad för mainstream och kostnadskänsliga applikationer, så den inkluderar inte inbyggda höghastighetsserspunkter.Det fokuserar istället på parallella gränssnitt och DDR -minnesstöd.

2. Kan LFEC3E-3Q208C omprogrammeras efter utplacering?

Ja.Som en FPGA är LFEC3E-3Q208C helt rekonfigurerbar, vilket möjliggör uppdateringar och designändringar även efter distributionen.Denna flexibilitet minskar långsiktiga underhållskostnader och förlänger produktlivscykler.

3. Hur hanterar LFEC3E-3Q208C felsökning och testning?

Enheten integrerar gränsskanning (IEEE 1149.1), logikanalys på chip (ISPTracy) och SPI-startblixtsupport.Dessa inbyggda verktyg förenklar felsökning och minskar behovet av extern testmaskinvara.

4. Kan LFEC3E-3Q208C förlänga livslängden för äldre hårdvarusystem?

Ja, tack vare dess breda I/O -kompatibilitet och protokollbryggningsfunktioner kan det gränssnitt äldre system med nyare komponenter, vilket hjälper företag att utöka användbarheten av befintlig hårdvara.

5. Vilka programmeringsverktyg krävs för LFEC3E-3Q208C?

Det är programmerat med Lattice's Diamond -programmerare eller ISPVM -system.Dessa verktyg stöder designpost, bitströmgenerering och enhetskonfiguration, vilket gör att arbetsflödet strömlinjeformas.

AD73311LARS: Datablad, funktioner, pinout- och programmeringsguide

på 2025/08/28

EPM1270F256C4N MAX II CPLD Översikt: Funktioner, specifikationer och applikationer

på 2025/08/28

Populära inlägg

-

Komplexa instruktionsuppsättningsdatorer: Hur de ändrade datoranvändning?

på 8000/04/19 147784

-

USB-C-pinout och funktioner

på 2000/04/19 112077

-

Använda Xilinx Unified Simulation Primitives: En omfattande guide till FPGA -design och simulering

på 1600/04/19 111352

-

Strömförsörjningsspänningar i elektronik: Betydelsen av VCC, VDD, VEE, VSS och GND

på 0400/04/19 83844

-

RJ45 -anslutningsguide: Pinout, ledningar, kabeltyper och användningar

på 1970/01/1 79648

-

Den ultimata guiden för trådfärgkoder i moderna elektriska system

Hur våra elektriska system använder färger är inte bara för utseende.Varje trådfärg indikerar nu en specifik funktion, vilket gör det lättare att identifiera och hantera elektriska komponenter korr...på 1970/01/1 67020

-

Purge Valve Guide: Funktion, symtom, testning och ersättning för optimal motorprestanda

Purge -ventilen är en viktig del av bilens system som hjälper till att hålla luften ren genom att hantera bränsleångor innan de kan fly in i atmosfären.Detta hjälper inte bara miljön genom att mins...på 1970/01/1 63140

-

Kvalitet (Q) Faktor: Ekvationer och applikationer

Kvalitetsfaktorn, eller 'Q', är viktig när man kontrollerar hur väl induktorer och resonatorer arbetar i elektroniska system som använder radiofrekvenser (RF).'Q' mäter hur väl en krets minimerar e...på 1970/01/1 63071

-

Uppnå toppprestanda med den maximala kraftöverföringssatsen

Den maximala kraftöverföringssatsen förklarar hur energi från en källa, till exempel ett batteri eller generator, flyter till en ansluten belastning.Det visar det exakta tillståndet där lasten får ...på 1970/01/1 54099

-

A23 -batterispecifikationer och kompatibilitet

A23-batteriet är ett litet, cylinderformat batteri med högspänning.Även kallad 23A, 23AE eller MN21, den körs vid 12 volt och mycket högre än AA- eller AAA -batterier.Dess speciella design...på 1970/01/1 52234