LVPECL förklaras: En guide till lågspännings positiv emitterkopplad logik

Positiv emitterkopplad logik (LVPECL) med låg spänningar står som en viktig utveckling inom digital logikteknik, skräddarsydd för att möta kraven från lågspänningsmiljöer.LVPECL, som arbetar med 3,3V eller 2,5V, utvecklas från den traditionella positiva emitterkopplade logiken (PECL), som förlitar sig på en 5,0V strömförsörjning.Denna förskjutning belyser den växande betoningen på energieffektiva lösningar som blandar hög prestanda med minskad kraftförbrukning.LVPECL är rotad i den historiska utvecklingen av emitterkopplad logik (ECL) och erbjuder distinkta fördelar i höghastighetsapplikationer, inklusive telekommunikation och dator, där energieffektivitet och signalintegritet är allvarliga.Den här artikeln gräver in i funktioner, fördelar och designhänsyn till LVPECL och belyser dess transformativa roll i modern elektronik.Från praktiska tillämpningar till tekniska distinktioner, upptäck hur LVPECL formar framtiden för digitala system.

Katalog

Klassificering av ECL

|

Typ |

Vcc |

Vå |

|

Pek |

5.0 V |

0,0 V |

|

Lvpecl |

3,3 v |

0,0 V |

|

2,5VPECL |

2,5 v |

0,0 V |

|

2.5VNECL |

0,0 V |

-2,5 v |

|

Lvnecl |

0,0 V |

-3.3 v |

|

Nekl |

0,0 V |

-5,0 v |

Fördelar med ECL/PECL/LVPECL -logik

• ECL -logiken sticker ut på grund av dess anmärkningsvärt låga produktionsimpedans och faller i allmänhet mellan 6 till 8 ohm.Denna funktion är i kombination med en exceptionellt hög inmatningsimpedans som kan betraktas som nästan oändlig.Sådana egenskaper ger ECL emponerande körfunktioner, vilket gör det möjligt att hantera överföringslinjer med karakteristiska impedanser från 50 till 130 ohm utan att avsevärt förnedra AC -prestanda.Möjligheten att upprätthålla signalintegritet över långa avstånd är mestadels aktiv i applikationer som ledning av backplan och omfattande kabelkörningar, där bevarande av signalkvalitet är dominerande.

• ECL -enheternas motståndskraft mot fluktuationer i spänning och temperatur är en annan anmärkningsvärd egenskap som skiljer dem från TTL- och CMOS -tekniker.Denna stabilitet visar sig vara fördelaktig i miljöer med olika förhållanden, vilket säkerställer konsekvent prestanda.Dessutom uppvisar de klockor som produceras av ECL-klockdrivare överlägsen synkronisering och minimerad skev, som är användbara för höghastighetsdataöverföringar.Precisionen i tidpunkten bidrar till förbättrad övergripande systemprestanda, mestadels i applikationer som kräver strikta tidsbegränsningar.

• I jämförelsen av ECL med andra signalmetoder uppstår en tydlig åtskillnad när det gäller frekvensstöd.ECL kan skickligt hantera frekvenser som överstiger 10 GHz, medan LVD -skivor vanligtvis takar runt 1,5 GHz.Denna kapacitet placerar ECL som ett formidabelt val för höghastighetsapplikationer, med operativa hastigheter som överträffar 5GHz och förseningar upprätthålls konsekvent under 1NS.Sådana prestandametriker gör ECL särskilt fördelaktigt för små till medelstora integrerade kretsar och digitala system för ultrahöjd hastighet, där varje nanosekund är viktig.

• ECL: s kompatibilitet med ett bredare spektrum av transmissionslinjeimpedanser ger en anmärkningsvärd fördel.Till skillnad från LVD-skivor, som kräver ett specifikt 100-ohm-avslutningsmotstånd för att upprätthålla signalintegritet, minskar ECL: s anpassningsförmåga till olika impedanser sannolikheten för signalreflektion och tillhörande komplikationer.Denna flexibilitet effektiviserar inte bara designhänsyn utan stärker också tillförlitligheten mellan olika applikationer.Kapaciteten att fungera effektivt över en rad impedanser ger dig möjlighet att integrera ECL i en bredare variation av system utan de stränga kraven som vanligtvis är kopplade till andra tekniker.

Nackdelar av ECL/PECL/LVPECL -logik

Medan Emitter-kopplad logik (ECL) har imponerande fördelar i höghastighetsapplikationer, har den också anmärkningsvärda nackdelar som motiverar uppmärksamhet.De primära frågorna inkluderar förhöjd kraftförbrukning, en begränsad tolerans för brus och en sårbarhet för yttre störningar.Den logiska svängningen i ECL -kretsar är begränsad till bara 0,8V, i kombination med en DC -brusolerans på bara 200 mV.Denna karakteristik belyser avvägningen där ECL: s exceptionella hastighetsförmåga kommer på bekostnad av krafteffektivitet och motståndskraft mot brusstörningar.I faktiska scenarier kan detta utgöra utmaningar, särskilt i miljöer där hantering av strömförbrukning är riskabelt eller där det är av största vikt att upprätthålla signalintegritet.

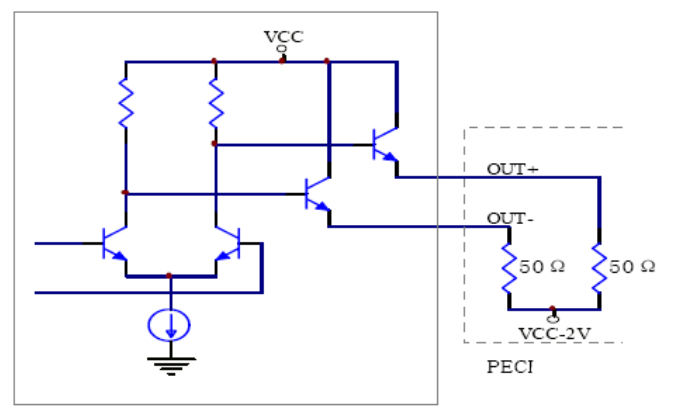

För positiv emitterkopplad logik (PECL) är standardutgångsbelastningen inställd på 50 ohm med en matningsspänning på VCC-2V.Under dessa parametrar är de typiska statiska nivåerna för OUT+ och OUT- VCC-1.3V, med en utgångsström på 14mA.Även om denna konfiguration visar sig vara effektiv för vissa applikationer, kan den inte anpassa sig väl till alla situationer, särskilt när man tar hänsyn till komplexiteten i termisk hantering och implikationerna av kraftfördelning förknippade med dessa utgångsnivåer.

PECL -utgångskretsstruktur

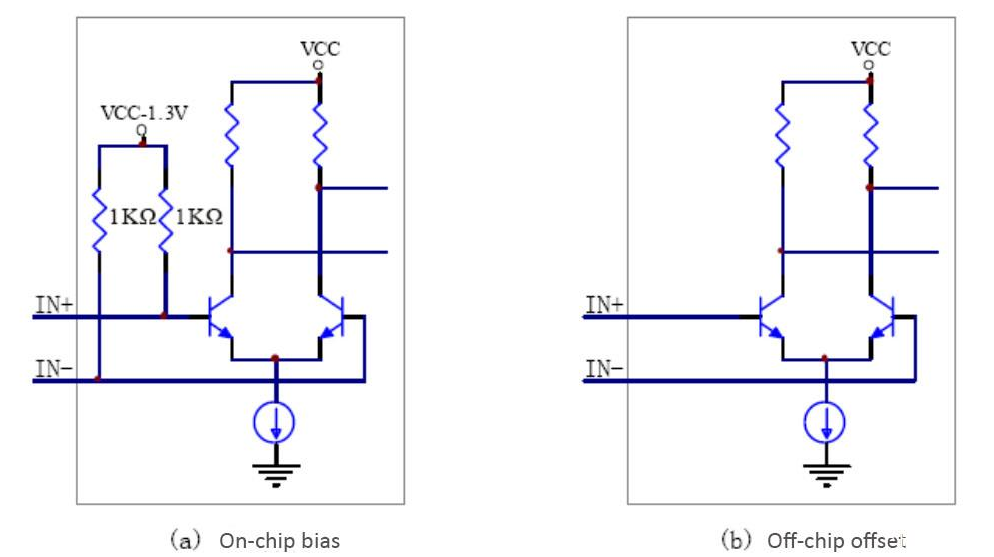

Inmatningen av PECL är ett differentiellt par med en hög inmatningsimpedans.För att uppnå den maximala dynamiska inmatningssignalnivån måste den vanliga lägesspänningen för detta differentiella par vara partisk till VCC - 1.3V.Vissa chips inkluderar en integrerad förspänningskrets, vilket möjliggör direktanslutning utan ytterligare komponenter.För chips utan denna inbyggda förspänningskrets måste emellertid en extern DC-förspänning appliceras under användning.

PECL -ingångskretsstruktur

Logiknivå standard för PECL

|

Parameter |

Skick |

Min |

Typisk |

Max |

Enhet |

|

Utgångshög |

TA = 0 ° C ~ 85 ° C |

VCC - 1.025 |

- |

VCC - 0,88 |

V |

|

TA = 40 ° C |

VCC - 1.085 |

- |

VCC - 0,88 |

V |

|

|

Utgång låg |

TA = 0 ° C ~ 85 ° C |

VCC - 1.81 |

- |

VCC - 1.62 |

V |

|

TA = 40 ° C |

VCC - 1.83 |

- |

VCC - 1.55 |

V |

|

|

Input hög |

- |

VCC - 1.16 |

- |

VCC - 0,88 |

V |

|

Input låg |

- |

VCC - 1.81 |

- |

VCC - 1.48 |

V |

Om oss

ALLELCO LIMITED

Läs mer

Snabb förfrågan

Skicka en förfrågan, vi svarar omedelbart.

4N25 OPTOCOUPLER: Funktioner, pinout och ekvivalenter

på 2024/12/27

D882 Transistor förklarade: pinout, konfiguration och säker användningstips

på 2024/12/27

Populära inlägg

-

Komplexa instruktionsuppsättningsdatorer: Hur de ändrade datoranvändning?

på 8000/04/19 147782

-

USB-C-pinout och funktioner

på 2000/04/19 112062

-

Använda Xilinx Unified Simulation Primitives: En omfattande guide till FPGA -design och simulering

på 1600/04/19 111352

-

Strömförsörjningsspänningar i elektronik: Betydelsen av VCC, VDD, VEE, VSS och GND

på 0400/04/19 83818

-

RJ45 -anslutningsguide: Pinout, ledningar, kabeltyper och användningar

på 1970/01/1 79635

-

Den ultimata guiden för trådfärgkoder i moderna elektriska system

Hur våra elektriska system använder färger är inte bara för utseende.Varje trådfärg indikerar nu en specifik funktion, vilket gör det lättare att identifiera och hantera elektriska komponenter korr...på 1970/01/1 66999

-

Purge Valve Guide: Funktion, symtom, testning och ersättning för optimal motorprestanda

Purge -ventilen är en viktig del av bilens system som hjälper till att hålla luften ren genom att hantera bränsleångor innan de kan fly in i atmosfären.Detta hjälper inte bara miljön genom att mins...på 1970/01/1 63124

-

Kvalitet (Q) Faktor: Ekvationer och applikationer

Kvalitetsfaktorn, eller 'Q', är viktig när man kontrollerar hur väl induktorer och resonatorer arbetar i elektroniska system som använder radiofrekvenser (RF).'Q' mäter hur väl en krets minimerar e...på 1970/01/1 63060

-

Uppnå toppprestanda med den maximala kraftöverföringssatsen

Den maximala kraftöverföringssatsen förklarar hur energi från en källa, till exempel ett batteri eller generator, flyter till en ansluten belastning.Det visar det exakta tillståndet där lasten får ...på 1970/01/1 54097

-

A23 -batterispecifikationer och kompatibilitet

A23-batteriet är ett litet, cylinderformat batteri med högspänning.Även kallad 23A, 23AE eller MN21, den körs vid 12 volt och mycket högre än AA- eller AAA -batterier.Dess speciella design...på 1970/01/1 52208