Lågspänning CMOS (LVCMOS): En omfattande guide till teknik, design och applikationer

Den här guiden undersöker CMOS -teknik med låg spänning (LVCMOS), en viktig innovation inom modern elektronik som hjälper till att minska kraftförbrukningen och stödja hållbar design.Det täcker grunderna i CMOS -teknik, praktiska designtips och dess applikationer inom konsument- och industriella enheter.Katalog

Förstå CMOS -teknik

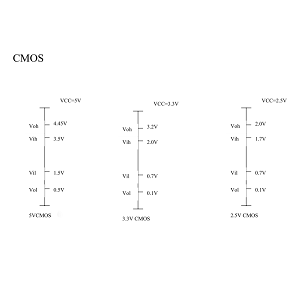

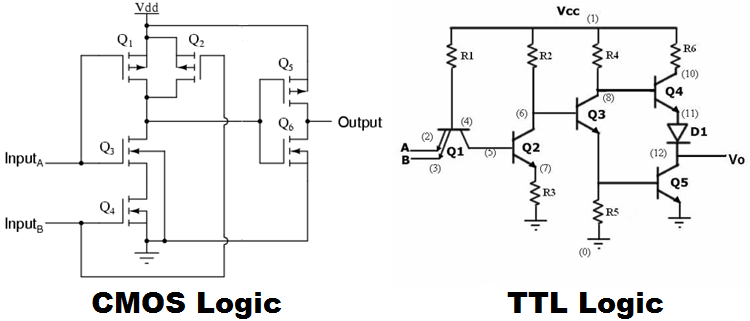

CMOS (kompletterande metalloxid-halvledare) teknik är en kärna i digital logik, som kombinerar PMOS- och NMOS-transistorer för att leverera hög brusbeständighet, låg effektförbrukning och effektiv energihantering.Dess förmåga att växla mellan logikstillstånd med minimal effektförlust gör det överlägset äldre tekniker som TTL (transistor-transistor logik), vilket erbjuder bättre brusmarginaler och högre ingångsimpedans.Standard CMOS -modeller, som 3.3V och 2.5V LVCMO, anpassar sig till olika spänningsbehov, vilket förbättrar kompatibilitet och systemprestanda.Utmaningar som spärrfenomen, utlöses av felaktig ingångsspänning, visar emellertid behovet av noggrann kretsdesign för att säkerställa hållbarhet.Utöver sina tekniska fördelar är CMOS-innovation i linje med hållbarhetsmålen, minskar energianvändningen och termisk produktion för att stödja miljövänliga elektroniska framsteg.

Fenomen

Lock-in-fenomenet förekommer i CMOS-kretsar när en plötslig spik i strömmen får intern kraftförbrukning att stiga okontrollerat.Detta tillstånd fortsätter tills strömförsörjningen avbryts.Ström kan överstiga 40MA, vilket hotar chipets stabilitet och gör omedelbara åtgärder nödvändiga för att lösa problemet.

Hur förhindrar man inlåstfenomenet?

Flera metoder kan hjälpa till att förhindra detta skadliga tillstånd:

• Klämkretsar: Placera klämkretsar vid ingången och utgången.Dessa kretsar håller spänningen inom säkra gränser och skyddar chipet från farliga spänningsnivåer som kan utlösa inlåsning.

• Avkopplingskretsar: Lägg till frikopplingskretsar till kraftingångar.Dessa kretsar minskar plötsliga spänningsvågor genom att jämna ut fluktuationer, vilket förbättrar kretsstabiliteten.

• Strömbegränsande motstånd: Använd ett strömbegränsande motstånd mellan VDD och extern kraftkälla.Denna enkla lösning styr strömflödet, håller det inom säkra gränser och förhindrar spikar som kan leda till inlåst.

• Hantering av flera strömförsörjningar: Korrekt hantering av strömförsörjning kan också bidra till att minska risken för inlåsning.

• Power Timing Protocol: Följ strukturerade power-up och power-down-procedurer.Slå på CMOS -kretsen innan du använder inmatningssignaler eller laster.Koppla först in ingångar och laddar först när du stänger av.Dessa steg förbättrar tillförlitligheten och förhindrar låsning.

Jämförelse av TTL -krets- och CMOS -kretsen

TTL (Transistor-Transistor Logic) kretsar är snabba, nuvarande drivna enheter med minimala förseningar av överföring (5-10 nanosekunder) men hög effektförbrukning, vilket gör dem mindre idealiska för energikänsliga applikationer.Å andra sidan fungerar CMO: er (kompletterande metalloxid-sememiconductor) kretsar med hjälp av spänningskontroll, vilket gör dem energieffektiva men långsammare (25-50 nanosekunder).Medan TTL: s hastighet passar tidskritiska uppgifter, är CMO: s effektivitet fördelaktigt för batteridrivna eller termiskt begränsade enheter.Valet mellan de två beror ofta på avvägningen mellan hastighet och energianvändning.Många kombinerar båda teknikerna för att optimera systemprestanda, utnyttja TTL för hastighetskritiska komponenter och CMO för energieffektiva områden, vilket skapar anpassningsbara och hållbara lösningar.

Om oss

ALLELCO LIMITED

Läs mer

Snabb förfrågan

Skicka en förfrågan, vi svarar omedelbart.

Utforska försenade låda slingor

på 2024/12/29

Mastering ModelSim: Verktyg för digital designsimulering

på 2024/12/29

Populära inlägg

-

Komplexa instruktionsuppsättningsdatorer: Hur de ändrade datoranvändning?

på 8000/04/18 147757

-

USB-C-pinout och funktioner

på 2000/04/18 111934

-

Använda Xilinx Unified Simulation Primitives: En omfattande guide till FPGA -design och simulering

på 1600/04/18 111349

-

Strömförsörjningsspänningar i elektronik: Betydelsen av VCC, VDD, VEE, VSS och GND

på 0400/04/18 83719

-

RJ45 -anslutningsguide: Pinout, ledningar, kabeltyper och användningar

på 1970/01/1 79508

-

Den ultimata guiden för trådfärgkoder i moderna elektriska system

Hur våra elektriska system använder färger är inte bara för utseende.Varje trådfärg indikerar nu en specifik funktion, vilket gör det lättare att identifiera och hantera elektriska komponenter korr...på 1970/01/1 66898

-

Kvalitet (Q) Faktor: Ekvationer och applikationer

Kvalitetsfaktorn, eller 'Q', är viktig när man kontrollerar hur väl induktorer och resonatorer arbetar i elektroniska system som använder radiofrekvenser (RF).'Q' mäter hur väl en krets minimerar e...på 1970/01/1 63010

-

Purge Valve Guide: Funktion, symtom, testning och ersättning för optimal motorprestanda

Purge -ventilen är en viktig del av bilens system som hjälper till att hålla luften ren genom att hantera bränsleångor innan de kan fly in i atmosfären.Detta hjälper inte bara miljön genom att mins...på 1970/01/1 63007

-

Uppnå toppprestanda med den maximala kraftöverföringssatsen

Den maximala kraftöverföringssatsen förklarar hur energi från en källa, till exempel ett batteri eller generator, flyter till en ansluten belastning.Det visar det exakta tillståndet där lasten får ...på 1970/01/1 54081

-

A23 -batterispecifikationer och kompatibilitet

A23-batteriet är ett litet, cylinderformat batteri med högspänning.Även kallad 23A, 23AE eller MN21, den körs vid 12 volt och mycket högre än AA- eller AAA -batterier.Dess speciella design...på 1970/01/1 52118