XC2C256-7TQ144C CPLD: Pinout, funktioner, programmering och databladguide

I den här guiden får du en tydlig titt på XC2C256-7TQ144C, en lågeffekt CPLD från Xilinx's Coolrunner-II-familj (nu AMD).Du lär dig om dess PIN-konfiguration, CAD-modeller och huvudfunktioner som logikkapacitet, I/O-alternativ, spänningsstöd och kraftbesparande funktioner.Vi kommer också att gå igenom dess arkitektur, I/V -kurva och specifikationer, följt av applikationer, liknande delar, programmeringssteg, fördelar och nackdelar, förpackningsinformation och tillverkarinformation så att du kan förstå exakt hur den här enheten passar in i dina projekt.Katalog

Vad är XC2C256-7TQ144C?

De XC2C256-7TQ144C är en lågeffekt CPLD (komplex programmerbar logikenhet) från Xilinx's CoolRunner-II-familj, nu en del av AMD.Den har 256 makroceller och finns i ett 144-stifts TQFP-paket, designat för snabb, deterministisk drift med minimal strömförbrukning.Den arbetar på en 1,8 V-kärna och erbjuder tillförlitlig prestanda i en kompakt formfaktor och är väl lämpad för mönster som kräver omedelbar kapacitet och effektiv logisk implementering.Som en del av den mångsidiga coolrunner-II-serien drar den nytta av en beprövad arkitektur och bred designkompatibilitet.

Letar du efter XC2C256-7TQ144C?Kontakta oss för att kontrollera nuvarande lager, ledtid och prissättning.

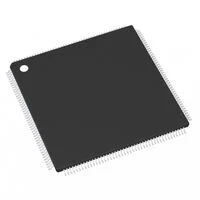

XC2C256-7TQ144C PIN-OUT DIAGRAM

XC2C256-7TQ144C PIN-OUT-diagrammet visar hur de 144 stiften är ordnade för kraft, mark, JTAG och användarprogrammerbara I/O-funktioner.De flesta stift är I/O, som kan konfigureras som ingångar eller utgångar och är jämnt fördelade för att stödja flexibel routing.VCC, VCCIO1, VCCIO2, Vaux och GND -stift placeras runt paketet för att tillhandahålla stabil kraftfördelning och flera I/O -spänningsalternativ.JTAG-stiften (TDI, TDO, TMS, TCK) grupperas för enkel programmering och testning i systemet.

XC2C256-7TQ144C CAD-modeller

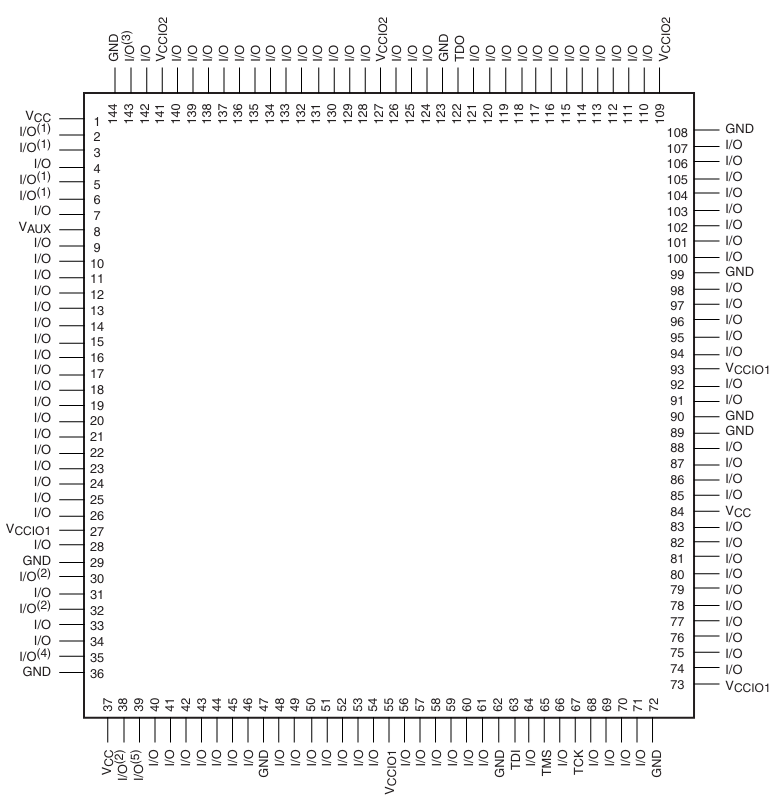

XC2C256-7TQ144C Symbol

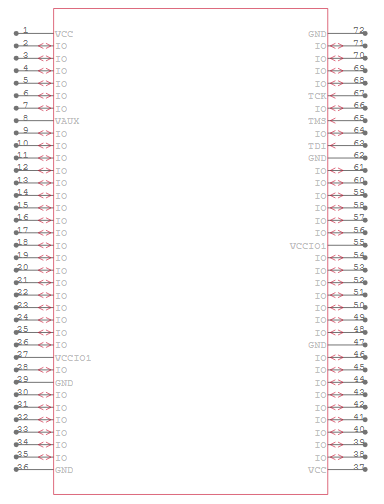

Xc2c256-7tq144c fotavtryck

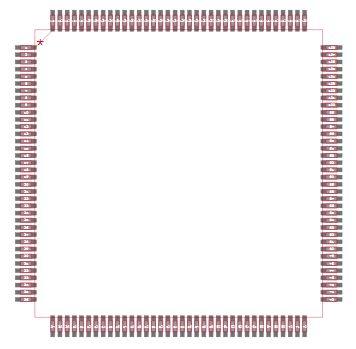

XC2C256-7TQ144C 3D-modell

XC2C256-7TQ144C-funktioner

• Enhetstyp och familj

XC2C256-7TQ144C är en komplex programmerbar logikenhet (CPLD) som tillhör familjen CoolRunner-II utvecklad av Xilinx (nu AMD).Den är utformad för låg effektförbrukning samtidigt som den är snabb, deterministisk logikprestanda, vilket gör den idealisk för kontrolllogik och gränssnittsapplikationer.

• Logikkapacitet

Den här enheten innehåller 256 makroceller, som är de programmerbara logikresurserna i CPLD.Dessa makroceller kan konfigureras för att implementera olika kombinations- och sekventiella logikfunktioner, vilket ger måttlig kapacitet för kontroll, limlogik och bussgränssnitt.

• Logikblock (funktionsblock)

Den integrerar 16 funktionsblock som organiserar och hanterar grupper av makroceller.Varje block tillhandahåller lokala sammankopplings- och produkttidsresurser, vilket möjliggör flexibel logikimplementering och effektiv routing inom enheten.

• Användare I/O -stift

XC2C256-7TQ144C erbjuder upp till 118 användarkonfigurerbara I/O-stift i sitt TQFP-144-paket.Detta höga PIN-räkning gör det möjligt för enheten att gränssnitt med flera delsystem samtidigt, vilket gör den lämplig för komplexa styrelsemönster.

• Kärnspänning (VCC)

Kärnan fungerar vid en nominell 1,8 V (1,7 V till 1,9 V -intervall), vilket hjälper till att minska strömförbrukningen jämfört med äldre 5 V CPLD.Denna lägre spänning är användbar i moderna digitala system med blandad spänningar.

• Multi-spänning I/O-stöd

I/O -bankerna stöder flera spänningsstandarder inklusive 1,5 V, 1,8 V, 2,5 V och 3,3 V. Denna flexibilitet gör det möjligt för CPLD att direkt gränssnittet med komponenter som arbetar vid olika spänningsnivåer utan externa nivåskiftare.

• Höghastighetsoperation

Med en typisk fördröjning av stift-till-pin-förökning på cirka 5,7 ns (hastighetskvalitet “-7”) levererar enheten snabb, deterministisk prestanda.Detta gör det lämpligt för tidskritiska applikationer som adressavkodning, busskiljedom och kontroll.

• Låg effektförbrukning

CoolRunner-II-serien är känd för extremt låga standby-strömmar, ofta i mikroampområdet.Denna låga statiska kraft, i kombination med dynamiska kraftbesparande funktioner, tillåter XC2C256-7TQ144C att användas effektivt i batteridrivna eller alltid-på-system.

• Datagate Technology

Denna funktion gör det möjligt att greka av oanvända ingångar, förhindra onödig växling och minska dynamisk strömförbrukning.Det är värdefullt i applikationer där vissa signaler är inaktiva under långa perioder.

• JTAG-programmering i systemet

Enheten stöder IEEE 1149.1 (JTAG) och IEEE 1532 för programmering i systemet.Detta innebär att CPLD kan konfigureras, testas och omprogrammeras utan att ta bort den från styrelsen, förenkla utvecklingen och uppdateringarna.

• Avancerad klockstruktur

XC2C256-7TQ144C inkluderar flera globala klockor, klockdelare och dubbelkantiga utlösade register.Det tillhandahåller också global uppsättning/återställning och lokal klockning per macrocell, vilket ger flexibel kontroll över timing och synkronisering.

• Schmitt-trigger-ingångar

Valda ingångsstift kan konfigureras som Schmitt triggers för att förbättra brusimmunitet.Detta är användbart för att hantera långsamma eller bullriga insignaler utan att lägga till externa konditioneringskretsar.

• Flexibla utgångsfunktioner

Utgångarna stöder trestatsens drift, svängningsstyrning, busshållning, öppna avdragskonfigurationer och valfria pull-ups.Dessa alternativ gör det enkelt att anpassa CPLD till olika busstandarder och externa belastningsförhållanden.

• Advanced Interconnect Matrix (AIM)

En avancerad sammankopplingsmatris kopplar effektivt funktionsblock, vilket ger full produktterter routing över enheten.Detta förbättrar flexibiliteten för logikplacering och hjälper till att upprätthålla förutsägbar tidsföreställning.

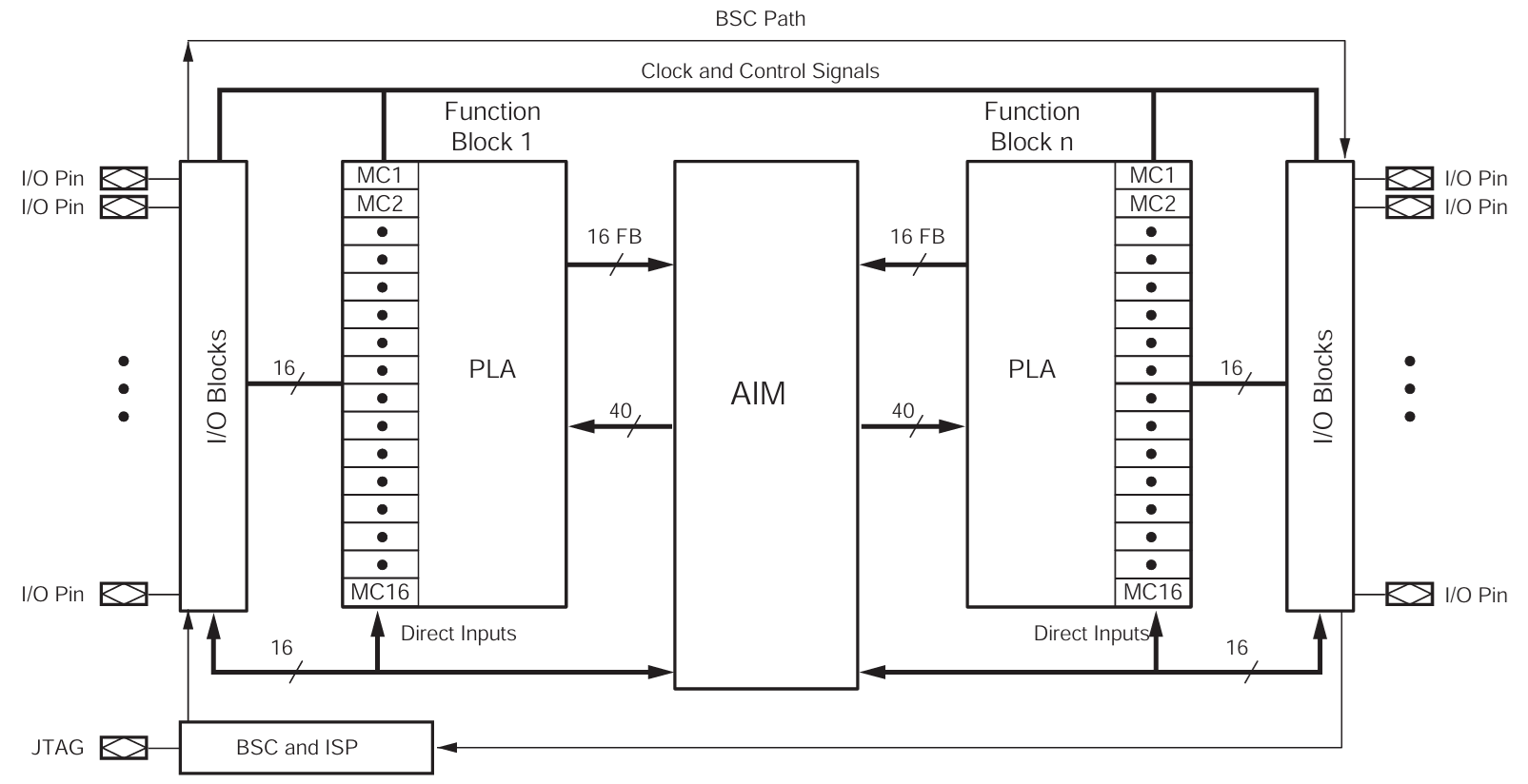

Coolrunner-II CPLD-arkitektur

Coolrunner-II CPLD-arkitekturen för XC2C256-7TQ144C är byggd kring funktionsblock, I/O-block och en avancerad samtrafikmatris (AIM).Varje funktionsblock innehåller makroceller och en programmerbar logikuppsättning (PLA) som implementerar användardefinierad logik, medan målet effektivt riktar signaler mellan block.I/O-blocken gränssnitt den interna logiken med externa stift och dedikerade JTAG- och BSC/ISP-kretsar stöd i systemprogrammering och testning.Denna strukturerade och sammankopplade arkitektur möjliggör snabb, deterministisk prestanda med låg effektförbrukning, vilket gör den idealisk för kontroll, gränssnitt och limlogik i digitala system.

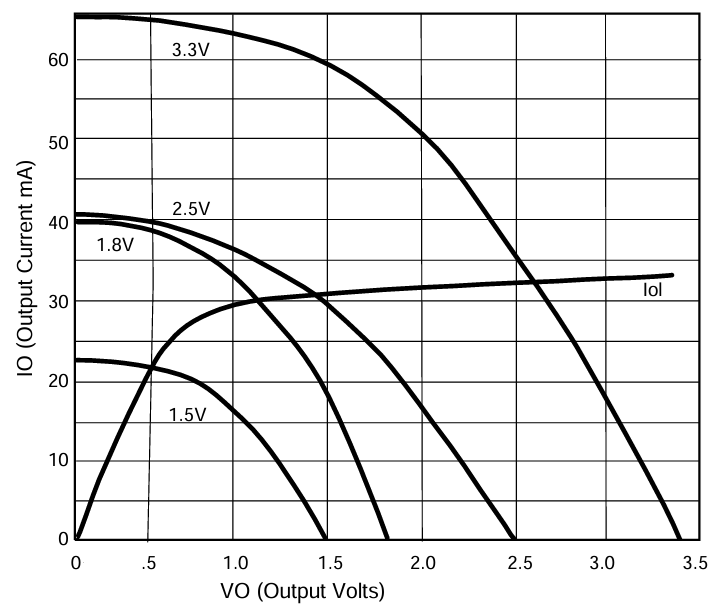

Typisk I/V -kurva för XC2C256

Den typiska I/V-kurvan för XC2C256-7TQ144C illustrerar förhållandet mellan utgångsspänning (VO) och utgångsström (IO) för olika I/O-matningsspänningar (1,5 V, 1,8 V, 2,5 V och 3,3 V).När matningsspänningen ökar kan enheten källa eller sjunka högre strömmar innan utgångsspänningen börjar sjunka avsevärt.Detta beteende är viktigt för att förstå CPLD: s drivförmåga vid gränssnitt med externa komponenter, vilket säkerställer att signalnivåerna förblir giltiga under belastning.Många använder denna kurva för att välja lämpliga I/O-spänningar och säkerställa tillförlitlig drift i applikationer som kräver specifika strömförvaltningsstyrkor.

XC2C256-7TQ144C-specifikationer

|

Typ |

Parameter |

|

Tillverkare |

Amd/xilinx |

|

Serie |

Coolrunner II |

|

Förpackning |

Bricka |

|

Delstatus |

Föråldrad |

|

Programmerbar typ |

I systemprogrammerbar |

|

Fördröjningstid TPD (1) Max |

6.7 NS |

|

Spänningsförsörjning - intern |

1,7 V ~ 1,9 V |

|

Antal logikelement/block |

16 |

|

Antal makroceller |

256 |

|

Antal grindar |

6000 |

|

Antal I/O |

118 |

|

Driftstemperatur |

0 ° C ~ 70 ° C (TA) |

|

Monteringstyp |

Ytfäste |

|

Förpackning / fodral |

144-LQFP

|

|

Leverantörspaket |

144-TQFP (20 × 20) |

|

Basproduktnummer |

Xc2c256 |

XC2C256-7TQ144C-applikationer

1. Limlogik och gränssnittsbryggning

XC2C256-7TQ144C är idealisk för implementering av limlogik, som ansluter och koordinerar signaler mellan olika digitala komponenter.Den kan hantera funktioner som adressavkodning, busskiljedom och protokollöversättning, vilket möjliggör smidig kommunikation mellan mikrokontroller, minne, sensorer och andra kringutrustning.Dess förutsägbara timing och snabba stift-till-stiftsförseningar säkerställer tillförlitlig gränssnitt även i komplexa brädkonstruktioner.

2. Lågkraft och batteridrivna enheter

Tack vare sin snabba nollkraft (FZP) teknik och mycket låg standby-ström är denna CPLD mycket lämplig för bärbar och batteridriven elektronik.Det kan förbli drivet kontinuerligt medan du konsumerar minimal energi, vilket gör den perfekt för alltid kontroll- eller övervakningskretsar.Du kan minska kraftanvändningen ytterligare med funktioner som Datagate, som minimerar dynamisk växling när ingångarna är inaktiva.

3. Kontrolllogik och sekvensering

Enheten utmärker sig vid implementering av ändliga tillståndsmaskiner, timingkontroll och signalsekvensering som krävs i många inbäddade system.Dess deterministiska, icke-flyktiga arkitektur gör det möjligt för kontrolllogiken att bli aktiv omedelbart efter power-up utan konfigurationsförseningar.Detta gör det till ett starkt val för återställningslogik, handskakningskretsar och andra tidskritiska kontrolluppgifter.

4. Inbäddat systemstöd och perifer logik

I inbäddade mönster kan XC2C256-7TQ144C fungera som ett anpassningsbart supportchip, implementera specialiserade gränssnitt eller utöka en mikrokontrollers kapacitet.Den kan hantera kommunikationsprotokoll som SPI, I²C eller UART, generera chipval eller hantera avbrottsrutning.Genom att avlasta dessa funktioner från CPU förenklar det firmwareutveckling och förbättrar den totala systemets prestanda.

XC2C256-7TQ144C Liknande delar

|

Specifikation |

XC2C256-7TQ144C |

XC2C256-7TQ144I |

XC2C256-7TQG144I |

XC2C256-7VQ100C |

XC2C256-7VQG100C |

XC2C256-6TQ144C |

|

Enhetsfamilj |

Coolrunner-ii cpld |

Coolrunner-ii cpld |

Coolrunner-ii cpld |

Coolrunner-ii cpld |

Coolrunner-ii cpld |

Coolrunner-ii cpld |

|

Logikdensitet (makroceller) |

256 |

256 |

256 |

256 |

256 |

256 |

|

Pakettyp |

TQFP-144 |

TQFP-144 |

TQFP-144 (PB-fri) |

VQFP-100 |

VQFP-100 (PB-fri) |

TQFP-144 |

|

Hastighetsgrad |

-7 |

-7 |

-7 |

-7 |

-7 |

-6 (snabbare) |

|

Temperaturområde |

Kommersiellt (0 - 70 ° C) |

Industriell (-40-85 ° C) |

Industriell (-40-85 ° C) |

Kommersiellt (0 - 70 ° C) |

Kommersiellt (0 - 70 ° C) |

Kommersiellt (0 - 70 ° C) |

|

I/O PIN -räkning |

118 |

118 |

118 |

80 |

80 |

118 |

|

Kärnspänning (VCC) |

1,8 v |

1,8 v |

1,8 v |

1,8 v |

1,8 v |

1,8 v |

|

I/O -spänningsstöd |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

|

Efterlevnad / PB-fri |

Standard |

Standard |

PB-FREE / ROHS |

Standard |

PB-FREE / ROHS |

Standard |

|

Skillnader |

Baslinje kommersiell version |

Industriell tempversion |

Industrial + PB-fri version |

Mindre paket, färre I/O |

PB-fri mindre version |

Snabbare tidsversion |

XC2C256-7TQ144C-programmeringssteg

Programmering av XC2C256-7TQ144C är en enkel process som innebär att du förbereder din design, genererar programmeringsfilen och laddar den i CPLD genom JTAG.Genom att följa varje steg noggrant kan du säkerställa en framgångsrik konfiguration och korrekt enhetsdrift på ditt kort.

1. Design och syntetisera

Du börjar med att skriva din logikdesign med HDL (VHDL eller Verilog) eller schematisk inträde.När du har slutfört designen kör du syntesprocessen, som konverterar din logik till enhetens interna struktur av makroceller och sammankopplingar.Detta steg säkerställer att din design är kompatibel med XC2C256 -arkitekturen och redo för implementering.

2. Plats och rutt / implementering (montering)

Därefter utför du plats och rutt, även känd som montering, som tilldelar din syntetiserade logik till faktiska fysiska makroceller och routingresurser i CPLD.Verktyget kontrollerar tidsbegränsningar, löser resursanvändning och optimerar vägar för att möta prestandan för din design.Detta säkerställer att kretsen kommer att köras pålitligt när den programmeras in i enheten.

3. Generera programmeringsfil

När implementeringen är klar genererar du programmeringsfilen (bit, sylt eller SVF -format) som innehåller exakta konfigurationsdata för enheten.Denna fil representerar hur varje macrocell, samtrafik och I/O är inställd för att implementera din logik.Att ha den här filen klar behövs innan du går vidare till den faktiska enhetsprogrammeringen.

4. JTAG / in-system-programmering

Slutligen ansluter du enheten till din dator med en JTAG -programmeringskabel och öppnar Xilinx Impact Tool (eller motsvarande).Du laddar sedan den genererade programmeringsfilen och laddar ner den till XC2C256-7TQ144C genom JTAG-stiften (TDI, TDO, TCK, TMS).När processen är klar börjar CPLD omedelbart arbeta med din programmerade logik utan att kräva en strömcykel eller externt konfigurationsminne.

XC2C256-7TQ144C Fördelar och nackdelar

Fördelar

• Mycket låg standby-kraft, idealisk för batteridrivna mönster.

• Instant-on-drift utan konfigurationsfördröjning.

• Förutsägbar tidpunkt för enklare designstängning.

• Ersätter flera diskreta logikchips, sparar utrymme och kostnad.

• Stöder flera I/O -spänningar utan externa nivåer.

Nackdelar

• Begränsad logikkapacitet jämfört med större CPLD eller FPGA.

• Ingen inbyggd DSP-, RAM-sändtagare.

• Att bli föråldrad och göra framtida inköp hårdare.

• Tak med lägre prestanda för höghastighetsapplikationer.

• Mindre routingflexibilitet för komplexa eller oregelbundna mönster.

XC2C256-7TQ144C förpackningsdimensioner

|

Typ |

Parameter |

|

Pakettyp |

TQFP-144 |

|

Paketets kroppsstorlek |

20 mm × 20 mm |

|

Blyplan |

0,5 mm |

|

Antal stift |

144 |

|

Pakethöjd (max) |

1,4 mm |

|

Pakettjocklek (nominell) |

1,0 mm |

|

Blylängd |

0,45 mm ~ 0,75 mm |

|

Ledningsbredd |

0,17 mm ~ 0,27 mm |

|

Monteringstyp |

Ytfäste |

|

Leverantörspaket |

144-TQFP (20 × 20) |

XC2C256-7TQ144C tillverkare

XC2C256-7TQ144C tillverkas av Xilinx, ett ledande företag inom programmerbara logiklösningar.Xilinx är allmänt erkänt för banbrytande FPGA- och CPLD-tekniker, vilket ger pålitliga och högpresterande enheter för industriella, kommersiella och konsumentapplikationer.Idag fungerar Xilinx som en del av Amd, fortsätter att leverera avancerade programmerbara logikprodukter med starkt långsiktigt stöd och innovation.

Slutsats

XC2C256-7TQ144C sticker ut för sin låga kraftförbrukning, snabb deterministiska prestanda och flexibilitet i flera spänningar I/O, vilket gör det till ett tillförlitligt val för moderna digitala mönster.Dess balanserade kombination av 256 makroceller, 118 I/O -stift och avancerad samtrafikarkitektur stöder ett brett utbud av kontroll-, gränssnitts- och limlogiska funktioner.Med stöd för programmering i systemet, Datagate-kraftbesparande funktioner och robusta I/O-konfigurationer integreras det smidigt i inbäddade system och miljöer med blandad spänningar.

Datablad pdf

XC2C256-7TQ144C Datablad:

Om oss

ALLELCO LIMITED

Läs mer

Snabb förfrågan

Skicka en förfrågan, vi svarar omedelbart.

Vanliga frågor [FAQ]

1. Kräver XC2C256-7TQ144C externt konfigurationsminne?

Nej. En av dess fördelar är omedelbar drift.Konfigurationen lagras internt, så den driver upp redo att köra utan något externt prom eller blixtminne.

2. Vilka programmeringsverktyg är kompatibla med XC2C256-7TQ144C?

Du kan programmera enheten med Xilinx Impact -programvara med en JTAG -programmeringskabel.Många använder också kompatibla tredjeparts JTAG-programmerare, men se till att de stöder IEEE 1149.1/1532 standarder.

3. Kan XC2C256-7TQ144C ersätta flera diskreta logik IC: er i din design?

Ja.Med sina 256 makroceller och flexibla I/O kan denna CPLD integrera flera limlogik- och kontrollfunktioner i en enhet, vilket hjälper dig att minska kortutrymme och komponentantal.

4. Är XC2C256-7TQ144C lämplig för batteriapplikationer med låg effekt?

Ja.Tack vare sin snabba nollkraft (FZP) -teknologi och mycket låg standby-ström är den idealisk för alltid kretsar, bärbara enheter och kraftkänsliga inbäddade system.

5. Kan du använda XC2C256-7TQ144C för höghastighetssignalbehandling?

Det är inte utformat för höghastighets DSP eller sändtagaruppgifter.Medan den levererar snabba förseningar i stift-till-stift, är det bäst lämpat för kontroll, gränssnitt och tidslogik, inte komplex databehandling.

EP2S60F672C4 FPGA: Funktioner, applikationer, programmering och databladguide

på 2025/10/4

EPM3256AFC256-7 CPLD Översikt: Funktioner, pinout, programmering och applikationer

på 2025/10/3

Populära inlägg

-

Komplexa instruktionsuppsättningsdatorer: Hur de ändrade datoranvändning?

på 8000/04/18 147770

-

USB-C-pinout och funktioner

på 2000/04/18 112006

-

Använda Xilinx Unified Simulation Primitives: En omfattande guide till FPGA -design och simulering

på 1600/04/18 111351

-

Strömförsörjningsspänningar i elektronik: Betydelsen av VCC, VDD, VEE, VSS och GND

på 0400/04/18 83768

-

RJ45 -anslutningsguide: Pinout, ledningar, kabeltyper och användningar

på 1970/01/1 79564

-

Den ultimata guiden för trådfärgkoder i moderna elektriska system

Hur våra elektriska system använder färger är inte bara för utseende.Varje trådfärg indikerar nu en specifik funktion, vilket gör det lättare att identifiera och hantera elektriska komponenter korr...på 1970/01/1 66959

-

Purge Valve Guide: Funktion, symtom, testning och ersättning för optimal motorprestanda

Purge -ventilen är en viktig del av bilens system som hjälper till att hålla luften ren genom att hantera bränsleångor innan de kan fly in i atmosfären.Detta hjälper inte bara miljön genom att mins...på 1970/01/1 63098

-

Kvalitet (Q) Faktor: Ekvationer och applikationer

Kvalitetsfaktorn, eller 'Q', är viktig när man kontrollerar hur väl induktorer och resonatorer arbetar i elektroniska system som använder radiofrekvenser (RF).'Q' mäter hur väl en krets minimerar e...på 1970/01/1 63040

-

Uppnå toppprestanda med den maximala kraftöverföringssatsen

Den maximala kraftöverföringssatsen förklarar hur energi från en källa, till exempel ett batteri eller generator, flyter till en ansluten belastning.Det visar det exakta tillståndet där lasten får ...på 1970/01/1 54096

-

A23 -batterispecifikationer och kompatibilitet

A23-batteriet är ett litet, cylinderformat batteri med högspänning.Även kallad 23A, 23AE eller MN21, den körs vid 12 volt och mycket högre än AA- eller AAA -batterier.Dess speciella design...på 1970/01/1 52184