XC2S50-5TQG144I FPGA: Funktioner, specifikationer, applikationer och programmeringsguide

XC2S50-5TQG144I är en flexibel och kraftfull FPGA (fältprogrammerbar grindarray) från AMD Xilinxs Spartan-II-familj.Det är utformat för digitala projekt som behöver anpassning, hastighet och tillförlitlighet.Den här guiden förklarar funktioner, specifikationer, programmeringsprocess och användningar av denna FPGA för att hjälpa dig att förstå hur du får ut det mesta.Katalog

XC2S50-5TQG144I Översikt

De XC2S50-5TQG144I är en Spartan-II FPGA från AMD Xilinx, designad för digitala projekt som behöver flexibilitet och prestanda.Den har 50 000 systemgrindar och 1 728 logikceller, vilket gör att den kan hantera komplexa uppgifter.Chipet innehåller 384 konfigurerbara logikblock (CLB) och 32 768 RAM -bitar, vilket ger det bra minne och bearbetningskraft.Med 92 ingångs-/utgång (I/O) -stift kan den enkelt ansluta till andra komponenter.Den finns i en 144-stifts tunn quad-platt-förpackning (TQFP), som är kompakt och lätt att använda.FPGA körs på 2,5V (med ett säkert intervall på 2,375V till 2,625V) och fungerar bra i temperaturer mellan -40 ° C och +100 ° C.Denna Spartan-II FPGA är tillverkad med 0,18-mikron-teknik, vilket gör den effektiv och pålitlig.Det är programmerbart, vilket innebär att du kan uppdatera dess funktioner efter behov.

För en kostnadseffektiv, högpresterande lösning är det det optimala valet att placera en bulkorder hos oss, vilket säkerställer överlägsen kvalitet.

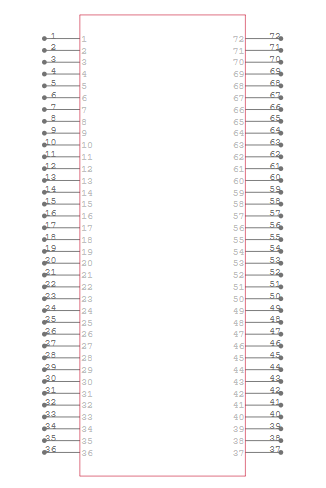

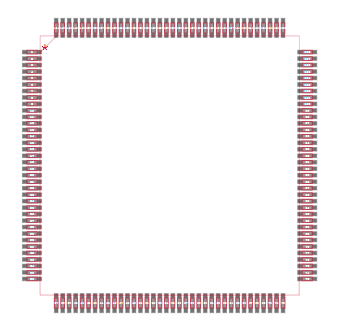

XC2S50-5TQG144I CAD-modeller

XC2S50-5TQG144I Symbol

XC2S50-5TQG144I FOTPRINT

XC2S50-5TQG144I 3D-modell

XC2S50-5TQG144I-funktioner

• Systemgrindar: XC2S50-5TQG144I FPGA erbjuder cirka 50 000 systemgrindar.Detta gör det möjligt att stödja komplexa digitala mönster och applikationer som kräver en betydande mängd logikbehandlingsfunktioner.

• Logikceller: Den här enheten innehåller 1 728 logikceller, som underlättar implementeringen av intrikata logikkonfigurationer och skapar olika digitala funktioner inom FPGA.

• Konfigurerbara logikblock (CLB): Den har 384 konfigurerbara logikblock (CLB), vilket ger grunden för FPGA: s logik.Dessa block kan programmeras och konfigureras om för att uppfylla specifika designkrav, vilket förbättrar enhetens totala mångsidighet.

• Ram: FPGA är utrustad med 32 768 bitar av intern RAM, och erbjuder effektiv datalagring och hämtningsfunktioner för uppgifter som involverar datamanipulation och tillfällig datalagring.

• I/O -stift: Med 92 I/O-stift säkerställer XC2S50-5TQG144I gott om extern anslutning, vilket gör att den kan gränssnitt med andra enheter och komponenter i ett system för omfattande systemintegration.

• Driftspänning: Enheten arbetar vid en nominell spänning på 2,5V, med ett acceptabelt intervall från 2.375V till 2.625V.Detta spänningsområde hjälper till att säkerställa stabil drift och pålitlig prestanda under olika elektriska förhållanden.

• Temperaturområde: XC2S50-5TQG144I är utformad för att fungera effektivt i ett brett temperaturområde, från -40 ° C till +100 ° C, vilket gör det lämpligt för distribution i miljöer med utmanande termiska förhållanden.

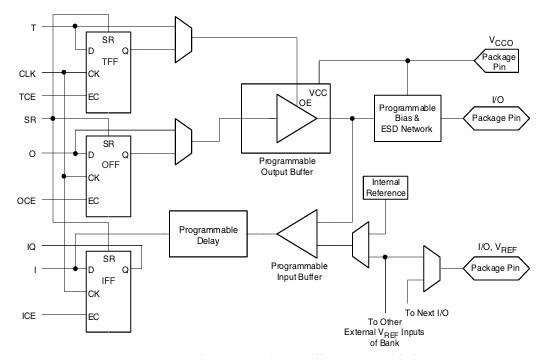

XC2S50-5TQG144I blockdiagram

Diagrammet visar hur signaler rör sig in och ut ur XC2S50-5TQG144I FPGA.Det förklarar hur chipet hanterar ingångs- och utgångssignaler för att kommunicera med andra komponenter.På utgångssida , signaler kommer inifrån FPGA och går igenom lagringsenheter som kallas flip-flops.Dessa flip-flops har data och ser till att signaler ändras vid rätt tidpunkt.Signalerna passerar sedan genom en programmerbar utgångsbuffert, som justerar hur stark signalen är och kontrollerar hur snabbt den förändras.Det finns också en switch (OE -kontroll) som bestämmer om utgången ska vara aktiv eller hålla sig av.En skyddskrets förhindrar skador från statisk elektricitet innan signalen når I/O -stiften, som ansluter till andra enheter.På inmatningssida, signaler från utsidan kommer in via den programmerbara ingångsbufferten, som bearbetar dem innan du skickar dem inuti FPGA.En programmerbar fördröjningsenhet hjälper till att justera signaltidpunkten så att allt förblir synkroniserat.FPGA kan också använda en intern referensspänning (VREF) för att matcha olika spänningsnivåer, vilket gör det lättare att arbeta med olika typer av kretsar.Vissa I/O -stift delar denna spänningsreferens för att hålla signaler stabila.Denna design hjälper FPGA att hantera signaler effektivt, vilket säkerställer korrekt timing, skydd och kompatibilitet med olika elektroniska komponenter.

XC2S50-5TQG144I-specifikationer

|

Typ |

Parameter |

|

Tillverkare |

AMD XILINX |

|

Serie |

Spartan®-II |

|

Förpackning |

Bricka |

|

Delstatus |

Föråldrad |

|

Antal laboratorier/clbs |

384 |

|

Antal logikelement/celler |

1728 |

|

Totala RAM -bitar |

32,768 |

|

Antal I/O |

92 |

|

Antal grindar |

50 000 |

|

Spänning - försörjning |

2.375V ~ 2.625V |

|

Monteringstyp |

Ytfäste |

|

Driftstemperatur |

-40 ° C ~ 100 ° C (TJ) |

|

Förpackning / fodral |

144-LQFP |

|

Leverantörspaket |

144-TQFP (20x20) |

|

Basproduktnummer |

Xc2s50 |

XC2S50-5TQG144I Applications

Inbäddade system

I inbäddade system tillhandahåller XC2S50-5TQG144I den nödvändiga logiken för mikrokontrollbaserade applikationer.Det används i stor utsträckning inom bilelektronik, bärbara enheter och småskaliga robotik för att förbättra funktionalitet och lyhördhet.

Signalbehandling

FPGA utmärker sig i signalbehandlingsuppgifter, där dess förmåga att utföra parallellbehandling krävs.Det är idealiskt för ljud- och videobehandling, telekommunikation och dataanalys, vilket ger hästkraften för att hantera komplexa algoritmer och höghastighetsdataströmmar.

Industrikontrollsystem

Industriella kontrollsystem drar nytta av denna FPGA: s robusthet och programmerbarhet, vilket gör det lämpligt för applikationer som processkontroll, maskinsautomation och systemövervakning.Dess tillförlitlighet säkerställer konsekvent prestanda i miljöer som kräver precision och operativ stabilitet.

Kommunikationssystem

I kommunikationssystem hjälper XC2S50-5TQG144I att hantera dataöverföring och mottagning, stödjande aktiviteter som signalmodulering och demodulering, protokollomvandling och nätverksrutning.Dess anpassningsförmåga är nyckeln till att utveckla telekommunikationsinfrastrukturer och nya trådlösa tekniker.

Prototypning och utveckling

FPGA används också i stor utsträckning för prototypning av digitala kretsar.Många använder det för att testa och förfina sina idéer före slutproduktionen, särskilt i komplexa ASIC och anpassade chipdesignprojekt.Denna kapacitet minskar utvecklingstiden och kostnaderna och påskyndar vägen från koncept till marknad.

XC2S50-5TQG144I Liknande delar

XC2S50-5TQG144I Fördelar

Kostnadseffektivitet

XC2S50-5TQG144I sticker ut för sin överkomliga priser och levererar fler funktioner per dollar än många konkurrerande FPGA.Denna kostnadseffektivitet uppnås genom avancerad processteknologi och en effektiv arkitektur, vilket möjliggör bredare distribution på kostnadskänsliga marknader.

Högpresterande I/O och förpackning

Denna FPGA stöder ett brett utbud av I/O-standarder och finns i olika kostnadseffektiva förpackningsalternativ.Dessa funktioner säkerställer att enheten kan integreras i flera applikationer utan att offra prestanda, vilket gör den idealisk för både high-end och volymdrivna marknader där gränssnittets mångsidighet och fysiska begränsningar är faktorer.

Systemnivåfunktioner

Utrustad med avancerade minneshanteringsfunktioner som distribuerad RAM och konfigurerbar block RAM, förbättrar XC2S50-5TQG144I datahanteringseffektivitet.Dessa funktioner underlättar komplexa datalagring och bearbetningsuppgifter, vilket ökar systemets totala prestanda och skalbarhet.

Omprogrammerbarhet

Omprogrammerbarheten för XC2S50-5TQG144I tillåter obegränsade modifieringar av dess konfiguration, vilket är fördelaktigt under utvecklingsfasen.Denna flexibilitet gör det möjligt att förfina mönster genom iterativa uppdateringar utan ytterligare hårdvarukostnader, främja innovation och minska tiden till slutprodukten.

XC2S50-5TQG144I-programmeringssteg

Programmering av XC2S50-5TQG144I FPGA från AMD XILINXs Spartan-II-serie involverar en strukturerad serie steg utformade för att effektivt översätta en digital design till en funktionell FPGA-konfiguration.Här är en integrerad och detaljerad guide som hjälper dig genom programmeringsprocessen:

1. Designpost

Börja med designinmatningsfasen, där du skapar din digitala logik med hjälp av ett hårdvarubeskrivningsspråk (HDL), till exempel VHDL eller Verilog.Detta första steg involverar att beskriva den funktionalitet och logik som du vill implementera i FPGA.Det krävs att din design är exakt och representerar exakt de avsedda operationerna för att säkerställa en framgångsrik syntes och implementering.

2. Syntes

I syntessteget använder du ett syntesverktyg för att konvertera din HDL -kod till en netlista.En netlista är en uppdelning av din design i ett format som innehåller olika sammankopplade logiska element som grindar och flip-flops.Denna process översätter din teoretiska design till en praktisk plan som FPGA kan förstå och implementera.

3. Implementering

Implementering involverar flera understeg: kartläggning, placering och routing.Kartläggning tilldelar elementen i din netlista till specifika logikblock inom FPGA.Placering bestämmer de fysiska platserna för dessa block på FPGA -chipet för att optimera prestanda och resursanvändning.Routing ansluter dessa block genom FPGA: s programmerbara sammankopplingsresurser.Denna fas säkerställer att designen uppfyller alla fysiska och prestandabegränsningar.

4. Begränsningsdefinition

Under designprocessen behövs det att definiera begränsningar.Begränsningar styr implementeringsverktygen genom att specificera krav som timing (hur snabbt FPGA ska fungera) och stiftuppdrag (som stift på FPGA kommer att ansluta till olika delar av din hårdvara).Dessa är formulerade i en användarbegränsningsfil (UCF), vilket hjälper till att finjustera designen för att uppfylla specifika operativa standarder.

5. Bitstream -generation

När din design framgångsrikt passerar genom implementeringsfasen är nästa steg att generera en Bitstream -fil.Den här filen innehåller alla konfigurationsdata som behövs av FPGA för att utföra designen.Bitstream är den slutliga utgången från programmeringsprocessen och representerar det kompletta, programmerade tillståndet för FPGA.

6. Enhetsprogrammering

Det sista steget är att ladda bitströmmen i XC2S50-5TQG144I FPGA, som kan göras med olika konfigurationslägen beroende på din installation.I Master Serial Mode, FPGA läser autonomt konfigurationsdata från en bifogad seriell prom (programmerbart skrivskyddsminne). Slavserieläge Tillåter en extern master -enhet, till exempel en mikrokontroller, att mata FPGA -konfigurationsdata seriellt. Slavparallellläge Aktiverar höghastighetsprogrammering genom att leverera konfigurationsdata parallellt från en extern master-enhet.Slutligen, Gränsskanning (JTAG) -läge använder JTAG -gränssnittet för både programmering och testning, vilket gör det användbart under utveckling för iterativ felsökning och verifiering.

XC2S50-5TQG144I förpackningsdimensioner

Den XC2S50-5TQG144I är en fältprogrammerbar grindarray (FPGA) från Xilinx's Spartan-II-familj, inrymt i en 144-stifts tunt fyrdubblar (TQFP) -paket.Detta paket mäter 20 mm x 20 mm.

XC2S50-5TQG144I-tillverkare

XC2S50-5TQG144I är en FPGA från familjen Spartan-II, tillverkad av AMD Xilinx.Xilinx, nu en del av Amd, är ett ledande halvledarföretag som specialiserat sig på FPGA, adaptiva SOC: er och andra programmerbara logikenheter.XC2S50-5TQG144I utvecklades ursprungligen under Xilinx Spartan-II-serien och erbjuder 50 000 systemgrindar och 1 728 logikceller, designade för högpresterande men ändå kostnadseffektiva tillämpningar.Med Xilinx förvärv av AMD fortsätter företaget att stödja äldre produkter som Spartan-II-serien samtidigt som de främjar nyare FPGA-arkitekturer.Emellertid är XC2S50-5TQG144I en äldre generationens FPGA och kan möta eventuell föråldring när AMD Xilinx skiftar fokus till mer avancerade FPGA-familjer.

Slutsats

XC2S50-5TQG144I FPGA är ett kostnadseffektivt och omprogrammerbart chip som erbjuder bra prestanda och flexibilitet.Det används ofta i inbäddade system, industriella maskiner och kommunikationsnätverk på grund av dess höghastighetsbehandling och starka anslutningsalternativ.Med sin förmåga att programmeras och uppdateras hjälper denna FPGA att testa och utveckla nya idéer före slutproduktionen.Även om nyare FPGA: er finns tillgängliga, förblir denna modell ett solid val för projekt som behöver en pålitlig och prisvärd FPGA -lösning.Den här guiden ger en tydlig och enkel översikt över FPGA: s funktioner, användningsområden och programmeringsprocessen, vilket gör den till en värdefull resurs för alla.

Om oss

ALLELCO LIMITED

Läs mer

Snabb förfrågan

Skicka en förfrågan, vi svarar omedelbart.

Vanliga frågor [FAQ]

1. Kan jag använda XC2S50-5TQG144I för höghastighetsapplikationer?

XC2S50-5TQG144I stöder hastigheter upp till 200 MHz, vilket gör den lämplig för de flesta inbäddade och industriella applikationer.Men om ditt projekt kräver höghastighetsgränssnitt som PCIe- eller DDR-minne, kan du behöva en mer avancerad FPGA som den Spartan-6 eller Artix-7-serien.

2. Hur jämför XC2S50-5TQG144I med den nyare Spartan-3 eller Spartan-6 FPGAS?

Medan nyare FPGA: er som Spartan-3 eller Spartan-6 erbjuder förbättrad prestanda, högre logikdensitet och ytterligare funktioner, förblir XC2S50-5TQG144I ett föredraget val för kostnadskänsliga projekt med måttlig komplexitet.Om du behöver äldre kompatibilitet eller en stabil leveranskedja är XC2S50-5TQG144I ett bra alternativ.

3. Vilka programmeringsverktyg är kompatibla med XC2S50-5TQG144I FPGA?

XC2S50-5TQG144I är programmerad med Xilinx ISE (integrerad mjukvarimiljö).Medan nyare Xilinx-verktyg som Vivado inte stöder familjen Spartan-II, tillhandahåller ISE all nödvändig design, syntes och programmeringsfunktioner för denna FPGA.

4. Kan jag migrera en befintlig Spartan-II-design till en nyare FPGA?

Ja, men det kräver modifieringar.De nyare familjerna Spartan-3 och Spartan-6 använder olika arkitektur-, spänningsnivåer och konfigurationsmetoder.Om du överväger migration kan vi hjälpa till att välja lämpliga alternativ och minimera designändringar.

5. Stöder XC2S50-5TQG144I JTAG-programmering?

S: Ja, FPGA stöder JTAG (IEEE 1149.1) Gränsskanningsprogrammering, vilket möjliggör enkel felsökning och konfiguration med ett standard JTAG -gränssnitt.Detta är användbart för både initial programmering och rekonfiguration utan externt minne.

XC4013XL-3PQ240C FPGA: Alternativ, specifikationer, applikationer och datablad

på 2025/03/18

RF -kraftförstärkare: Hur de fungerar, vilken typ är effektivare

på 2025/03/18

Populära inlägg

-

Komplexa instruktionsuppsättningsdatorer: Hur de ändrade datoranvändning?

på 8000/04/18 147766

-

USB-C-pinout och funktioner

på 2000/04/18 111994

-

Använda Xilinx Unified Simulation Primitives: En omfattande guide till FPGA -design och simulering

på 1600/04/18 111351

-

Strömförsörjningsspänningar i elektronik: Betydelsen av VCC, VDD, VEE, VSS och GND

på 0400/04/18 83758

-

RJ45 -anslutningsguide: Pinout, ledningar, kabeltyper och användningar

på 1970/01/1 79552

-

Den ultimata guiden för trådfärgkoder i moderna elektriska system

Hur våra elektriska system använder färger är inte bara för utseende.Varje trådfärg indikerar nu en specifik funktion, vilket gör det lättare att identifiera och hantera elektriska komponenter korr...på 1970/01/1 66952

-

Purge Valve Guide: Funktion, symtom, testning och ersättning för optimal motorprestanda

Purge -ventilen är en viktig del av bilens system som hjälper till att hålla luften ren genom att hantera bränsleångor innan de kan fly in i atmosfären.Detta hjälper inte bara miljön genom att mins...på 1970/01/1 63096

-

Kvalitet (Q) Faktor: Ekvationer och applikationer

Kvalitetsfaktorn, eller 'Q', är viktig när man kontrollerar hur väl induktorer och resonatorer arbetar i elektroniska system som använder radiofrekvenser (RF).'Q' mäter hur väl en krets minimerar e...på 1970/01/1 63028

-

Uppnå toppprestanda med den maximala kraftöverföringssatsen

Den maximala kraftöverföringssatsen förklarar hur energi från en källa, till exempel ett batteri eller generator, flyter till en ansluten belastning.Det visar det exakta tillståndet där lasten får ...på 1970/01/1 54094

-

A23 -batterispecifikationer och kompatibilitet

A23-batteriet är ett litet, cylinderformat batteri med högspänning.Även kallad 23A, 23AE eller MN21, den körs vid 12 volt och mycket högre än AA- eller AAA -batterier.Dess speciella design...på 1970/01/1 52176