EP20K100EFC324-1X FPGA: Funktioner, specifikationer, applikationer och programmeringsguide

EP20K100EFC324-1X är ett programmerbart chip (FPGA) från Intels Alta Apex-20Ke®-serie.Den är utformad för att hantera komplexa digitala kretsar och stöder höghastighetsdatabehandling.Den här guiden förklarar dess funktioner, specifikationer, hur man programmerar den och dess fördelar, vilket gör det till en användbar resurs för alla.Katalog

EP20K100EFC324-1X översikt

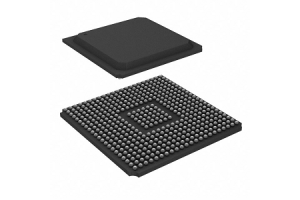

De EP20K100EFC324-1X är en del av Intels Alta Apex-20Ke®-serie, en fältprogrammerbar grindarray (FPGA) skräddarsydd för programmerbara logiska applikationer med hög densitet som kräver sofistikerade system-on-a-programmerbara-chip-integrationer.Denna enhet kännetecknas av sin integration av 4 160 logikelement eller celler och 416 logikmatrisblock (labb), vilket underlättar betydande konfigurerbarhet för olika digitala kretskonstruktioner.Det har också en betydande mängd inbäddat minne som rymmer krävande datalagringskrav inom FPGA.EP20K100EFC324-1X ytterligare förbättrar dess applikationens mångsidighet och erbjuder 246 I/O-stift och erbjuder ett betydande grindantal på cirka 263 000 motsvarande grindar och fungerar effektivt mellan 1,71V till 1,89V.Den är förpackad i en 324-boll fin-pitch bollnätarray (FBGA), som hjälper till att vara en robust fysisk integration i elektroniska enheter.

EP20K100EFC324-1X är det perfekta valet när du är redo att placera bulkorder hos oss för dina projekt eller produktlinjer.

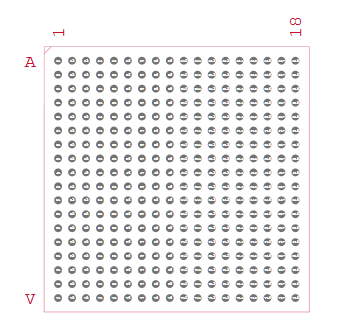

EP20K100EFC324-1X CAD-modeller

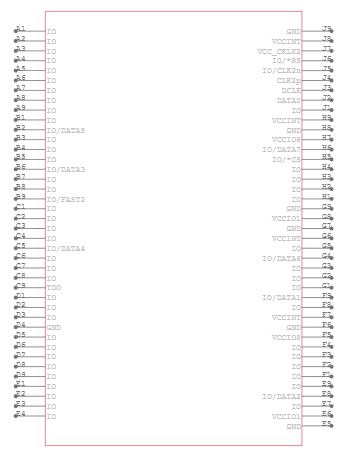

EP20K100EFC324-1X-symbol

EP20K100EFC324-1x fotavtryck

EP20K100EFC324-1X 3D-modell

EP20K100EFC324-1X-funktioner

• Hög logisk täthet: FPGA är utrustad med 4 160 logikelement (LES) och 416 logikmatrisblock (LAB).Denna höga täthet av logikceller möjliggör design och utförande av komplexa digitala kretsar och system inom ett enda chip, vilket gör det idealiskt för applikationer som kräver robusta logikbehandlingsfunktioner.

• Inbäddat minne: Erbjuder 53 248 RAM -bitar och ger denna FPGA betydande inbäddade minnesresurser.Den här funktionen är bra för applikationer som kräver snabb datalagring och hämtning, vilket möjliggör effektiv hantering av datakrävande uppgifter.

• Omfattande I/O -kapacitet: Med 246 ingångs-/utgångsstift säkerställer EP20K100EFC324-1X omfattande anslutnings- och gränssnittsalternativ.Detta breda sortiment av I/O -kapacitet gör det möjligt för den att enkelt ansluta till en mängd externa enheter och system, vilket förbättrar dess användbarhet i komplexa elektroniska enheter.

• Flerspänningsstöd: Enheten stöder ett kärnspänningsområde på 1,71V till 1,89V och har multivolt ™ I/O -gränssnitt.Detta gör att FPGA kan vara kompatibel med andra elektroniska komponenter som fungerar på olika logiknivåer, inklusive 1,8V, 2,5V, 3,3V och 5,0V, vilket ger stor flexibilitet i systemdesign.

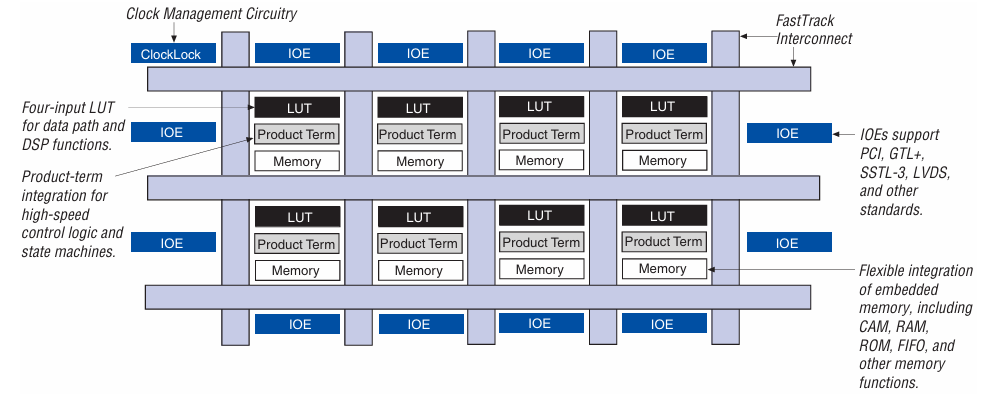

EP20K100EFC324-1X blockdiagram

De EP20K100EFC324-1X blockdiagram Representerar den interna strukturen för en FPGA -enhet (fältprogrammerbar grind) som visar upp dess olika funktionella enheter.Diagrammet består av sammankopplade logikblock, minneselement, klockhantering och I/O -element.Kärnan i designen är Logikuppsättningsblock (Labb), som innehåller Uppslagstabeller (LUTS) och produkttidsbaserad logik.Dessa element möjliggör flexibel logikimplementering, vilket gör FPGA lämplig för höghastighetsstyrningslogik, tillståndsmaskiner och DSP-funktioner.De FastTrack Interconnect Ger en höghastighetskommunikationsväg mellan logikelement, vilket säkerställer effektiv signalruttning i hela enheten.De Klockhanteringskretsar , inklusive klocklockfunktionen, säkerställer tillförlitlig och synkroniserad drift genom att stabilisera och distribuera klocksignaler över FPGA.De Input/utgångselement (IOE), placerat runt FPGA -tyget, fungerar som gränssnitt för extern kommunikation.Dessa IE: er stöder flera branschstandardprotokoll som PCI, Gtl+, SSTL-3och LVD -skivor, vilket gör det möjligt för FPGA att gränssnitt med olika externa system.Dessa IE: er säkerställer kompatibilitet med olika spänningsnivåer och signalstandarder, vilket förbättrar FPGA: s mångsidighet i inbäddade applikationer. Inbäddade minnesblock Ge flexibla lagringslösningar inom FPGA.Dessa minneselement kan fungera som Innehållsadresserbart minne (KAM), Slumpmässig åtkomstminne (Ram), Skrivskyddsminne (Rom), Först-i-första-ut (FIFO) buffertar och andra minnesstrukturer.Möjligheten att integrera minne direkt i FPGA -tyget förbättrar effektiviteten i databehandlingen, vilket minskar externa minnesberoenden och latens.

EP20K100EFC324-1X-specifikationer

|

Typ |

Parameter |

|

Tillverkare |

Intel |

|

Serie |

APEX-20KE® |

|

Förpackning |

Bricka |

|

Delstatus |

Föråldrad |

|

Antal laboratorier/clbs |

416 |

|

Antal logikelement/celler |

4160 |

|

Totala RAM -bitar |

53248 |

|

Antal I/O |

246 |

|

Antal grindar |

263000 |

|

Spänning - försörjning |

1,71V ~ 1,89V |

|

Monteringstyp |

Ytfäste |

|

Driftstemperatur |

0 ° C ~ 85 ° C (TJ) |

|

Förpackning / fodral |

324-bga |

|

Leverantörspaket |

324-FBGA (19x19) |

|

Basproduktnummer |

EP20K100 |

EP20K100EFC324-1X Applications

Nätverk och kommunikation

Denna FPGA är idealisk för nätverksutrustning som routrar och switchar, där den hanterar datarrutning, signalbehandling och protokollhantering.Dess höga logikdensitet och omfattande I/O-kapacitet gör det möjligt att stödja de komplexa, höghastighetsdataoperationer som krävs i modern kommunikationsinfrastruktur.

Industrikontrollsystem

I industrisektorn utmärker sig EP20K100EFC324-1X i automatiseringssystem.Dess programmerbarhet och robusta bearbetningsfunktioner möjliggör exakt kontroll och övervakning för att förbättra driftseffektiviteten och tillförlitligheten i tillverkningsprocesser.

Fordonselektronik

FPGA fungerar som en komponent i bilapplikationer, särskilt i Advanced Driver-Assistance Systems (ADAS) och infotainment-system i fordon.Det tillhandahåller den nödvändiga bearbetningskraften och anpassningsförmågan för att hantera data och stödja de sofistikerade funktioner som krävs i moderna fordon.

Konsumentelektronik

På grund av dess flexibilitet och höga prestanda finns EP20K100EFC324-1X också i konsumentelektronik som högupplöst tv-apparater och spelkonsoler.Det stöder komplexa funktionaliteter och AIDS i förkortande produktutvecklingscykler och möter den snabba efterfrågan på konsumentelektronikmarknaden.

Medicinsk utrustning

Inom det medicinska området bidrar denna FPGA till funktionaliteten för medicinsk avbildning och diagnostiska verktyg.Dess förmåga att bearbeta data med höga hastigheter säkerställer att dessa enheter kan leverera exakta och snabba diagnostiska resultat för effektiv medicinsk behandling och avbildning.

EP20K100EFC324-1X Liknande delar

EP20K100EFC324-1x programmeringssteg

För att effektivt programmera EP20K100EFC324-1X, en medlem av Alteras APEX-20KE® FPGA-serie, är det viktigt att följa en strukturerad steg av steg.Denna process säkerställer att din design effektivt översätts till ett format som FPGA kan köra.Nedan beskriver jag ett detaljerat tillvägagångssätt för att programmera denna FPGA -modell, integrera steg och modifieringar som är specifika för den här enheten.

1. Designpost

Börja med att skapa din digitala logikdesign.Använd hårdvarubeskrivning Språk (HDL) som VHDL eller Verilog, som gör att du kan beskriva hårdvarufunktionen och logiken i ditt system.Verktyg som Alteras Quartus II erbjuder en omfattande miljö för att skriva, testa och sammanställa din HDL -kod.Se till att din design är modulär, vilket gör det lättare att felsöka och skala.

2. Syntes

När din designpost är klar är nästa steg syntes, där HDL -koden översätts till en netlista.Den här netlistan representerar den sammankopplade listan över grindar, flip-flops och andra hårdvaruelement som utgör din design.Under syntesen är koden optimerad för den specifika arkitekturen för EP20K100EFC324-1X, vilket säkerställer att designen använder FPGA: s resurser effektivt.Verktyg som Synplify Pro eller syntesverktyget inom Quartus II kan användas för detta ändamål.Det är viktigt att fokusera på att optimera din design för att uppfylla tidpunkten och resursbegränsningarna.

3. Implementering

Efter syntes sker implementeringen.Detta steg involverar att kartlägga netlistan till den faktiska FPGA -hårdvaran.Det inkluderar placering av logikelementen i FPGA och dirigering av anslutningarna mellan dem.Quartus II -programvaran underlättar denna process genom sina implementeringsverktyg, som hanterar placering och routing för att möta önskade klockhastigheter och prestandametriker.Under implementeringen kan du behöva iterera på din design baserat på feedback från tidsanalysverktyg för att säkerställa att alla prestandakrav uppfylls.

4. Bitstream -generation

Efter framgångsrik implementering genererar nästa fas bitströmmen.Detta är den binära filen som kommer att laddas på FPGA.Bitstream innehåller konfigurerade data för varje programmerbart element i FPGA och ställer in enheten för att utföra funktionerna enligt din design.Quartus II -programvaran kan generera denna bitström, som sedan är redo att laddas ner till FPGA.

5. Programmera FPGA

Det sista steget är att programmera FPGA med den genererade bitströmmen.Detta kan göras med hjälp av en hårdvaruprogrammerare kompatibel med EP20K100EFC324-1X, till exempel USB-blaster.Anslut programmeraren till ditt utvecklingskort där FPGA är monterad och använd Quartus II -programmeringsverktyget för att överföra bitströmmen till FPGA.Detta steg laddar din design på FPGA, och den börjar fungera enligt den logik som definieras i din HDL -kod.

EP20K100EFC324-1X Fördelar

Hög integration

EP20K100EFC324-1X erbjuder höga integrationsfunktioner på grund av dess stora antal logikelement och inbäddat minne.Denna integration möjliggör konsolidering av flera funktionaliteter till en enda enhet.Som ett resultat kan system förenklas, vilket minskar det totala komponentantalet, det fysiska utrymmet som krävs och potentiella felpunkter i elektroniska konstruktioner.

Flexibel logikimplementering

Arkitekturen för EP20K100EFC324-1X stöder både uppslagstabell (LUT) och produktterminbaserad logik.Denna flexibilitet i logisk implementering gör det möjligt att optimera FPGA för ett brett spektrum av applikationer, från enkla logiska grindar till komplexa kombinationskretsar.Det ger en fördel när det gäller designens mångsidighet och kan rymma ett brett spektrum av digitala funktioner.

Avancerad samtrafikstruktur

FPGA har en hierarkisk sammankopplingsstruktur och inkluderar Local, MegalaB ™ och FastTrack® -sammankopplingar.Dessa specialiserade routingresurser förbättrar signalens routingeffektivitet och förbättrar enhetens totala prestanda.Denna avancerade sammankopplingsstruktur är bra för mönster som kräver höghastighetsdataöverföring och låg latens, vilket gör FPGA idealisk för högpresterande datoranvändning och telekommunikation.

Klockstyrelse

EP20K100EFC324-1X innehåller Clocklock och Clockboost-teknik, som hjälper till med effektiv klockhantering.Dessa funktioner hjälper till att bibehålla klocksignalens integritet i hela FPGA, minska jitter och förbättra signal pålitlighet.Effektiv klockhantering behövs för synkrona digitala kretsar, vilket säkerställer stabil och förutsägbar drift i olika miljöförhållanden.

Designflexibilitet

Den programmerbara karaktären av EP20K100EFC324-1X gör det möjligt att skräddarsy hårdvara till specifika behov och konfigurera FPGA för olika applikationer eller uppdateringar.Denna flexibilitet innebär att en enda FPGA kan användas över flera projekt, vilket är fördelaktigt i ett dynamiskt tekniskt landskap där kraven kan förändras snabbt.

Snabb prototyp

FPGA: er som EP20K100EFC324-1X Aktiverar snabb prototypning av digitala kretsar.Du kan utveckla och iterera mönster snabbt utan de långa ledtiderna förknippade med anpassad ASIC -utveckling.Denna förmåga att snabbt modellera och testa nya mönster påskyndar utvecklingsprocessen, vilket leder till snabbare innovation och förkortad tid till marknad.

Kostnadseffektivitet

Integrering av flera funktioner i en enda FPGA minskar behovet av ytterligare diskreta komponenter, vilket kan leda till kostnadsbesparingar i både upphandling och montering.Denna integration förenklar också tillverkningsprocessen och kan minska den övergripande systemkomplexiteten, vilket leder till lägre underhåll och uppgraderingskostnader under produktens livscykel.

Långsiktigt stöd

Den rekonfigurerbara aspekten av EP20K100EFC324-1X säkerställer att hårdvara kan uppdateras för att fixa buggar, förbättra prestanda eller lägga till nya funktioner utan att kräva fysisk hårdvaruförändringar.Detta långsiktiga stöd och anpassningsförmåga skyddar investeringar och gör det möjligt för enheter att förbli relevanta när nya standarder och teknik dyker upp.

EP20K100EFC324-1X Förpackningsdimensioner

EP20K100EFC324-1X är en FPGA från Alteras Apex-20Ke®-serie, inrymd i en 324-boll Fine Pitch Ball Grid Array (FBGA) paket.Dess förpackningsdimensioner är följande:

• Tonhöjd: 1 mm

• Längd × bredd: 19 mm × 19 mm

• Område: 361 mm²

EP20K100EFC324-1X Tillverkare

EP20K100EFC324-1X är en modell från APEX-20KE®-serien av fältprogrammerbara grindarrayer (FPGA) som ursprungligen utvecklats av Altera.Efter Intels förvärv av Altera 2015 blev denna FPGA och andra Altera -produkter en del av Intels omfattande programmerbara lösningsportfölj.Som ett resultat Intel Fortsätter att stödja Alteras produktlinjer medan de integrerar dem med sina egna avancerade teknikerbjudanden.Även om EP20K100EFC324-1X har klassificerats som föråldrad och inte längre är i produktion, upprätthålls dess arv under Intel, vilket rekommenderar nyare FPGA-modeller för nuvarande applikationer för att säkerställa långsiktigt stöd och tillgänglighet.

Slutsats

EP20K100EFC324-1X är en kraftfull och flexibel FPGA som gör det möjligt att skapa och testa anpassade digitala kretsar.Det erbjuder högpresterande, inbyggt minne och multi-spänningssupport, vilket gör det användbart i många branscher.Den här guiden har tagit dig genom huvudfunktionerna, designen och stegen för att programmera denna FPGA på ett enkelt sätt, så att du enkelt kan förstå och använda den.

Datablad pdf

EP20K100EFC324-1X Datablad:

Om oss

ALLELCO LIMITED

Läs mer

Snabb förfrågan

Skicka en förfrågan, vi svarar omedelbart.

Vanliga frågor [FAQ]

1. Hur jämför EP20K100EFC324-1X med nyare FPGA-modeller?

EP20K100EFC324-1X förblir en kraftfull FPGA för äldre system och industriella tillämpningar som kräver hög logisk densitet och flexibla I/O-kapacitet.Jämfört med moderna FPGA: er som Intels cyklon, arria eller stratix-serie, saknar det emellertid avancerad effekteffektivitet, höghastighetsändringar och AI-driven acceleration.Om du utformar ett nytt system kan vi föreslå motsvarande eller uppgraderade modeller.

2. Stödjer EP20K100EFC324-1X externa minnesgränssnitt som DDR eller SRAM?

Ja, EP20K100EFC324-1X stöder externa minnesgränssnitt, inklusive SRAM och SDRAM.Men det stöder inte naturligt DDR2/DDR3.Om gränssnittet med hög hastighetsminne krävs kan ytterligare extern logik eller en nyare FPGA vara nödvändig.

3. Kan jag konfigurera om EP20K100EFC324-1x flera gånger?

Ja, som alla FPGA: er är den här enheten helt omprogrammerbar.Men om du använder en flyktig konfiguration behöver du ett externt minne (t.ex. en seriell prom) för att behålla designen efter kraftcykling.

4. Kan jag programmera EP20K100EFC324-1x med Intel Quartus-programvara?

Ja, du kan programmera EP20K100EFC324-1X med Intel Quartus II (Legacy Versions), eftersom denna FPGA tillhör APEX-20KE®-familjen.Se till att din Quartus II -version stöder den här enheten, eftersom nyare Quartus Prime -utgåvor inte stöder Legacy FPGA.

5. Vilka krav på strömförsörjning ska jag överväga när jag använder EP20K100EFC324-1X?

EP20K100EFC324-1X fungerar med ett kärnspänningsområde på 1,71V till 1,89V.Den har också Multivolt ™ I/O -teknik, som stöder 1,8V, 2,5V, 3,3V och 5,0V logiknivåer.Se till att din strömförsörjning uppfyller dessa spänningskrav för stabil prestanda.

XCV200-6FG456C FPGA: Funktioner, specifikationer, programmering och applikationer

på 2025/03/20

Varför 0603 komponenter är populära inom modern elektronik

på 2025/03/20

Populära inlägg

-

Komplexa instruktionsuppsättningsdatorer: Hur de ändrade datoranvändning?

på 8000/04/18 147772

-

USB-C-pinout och funktioner

på 2000/04/18 112009

-

Använda Xilinx Unified Simulation Primitives: En omfattande guide till FPGA -design och simulering

på 1600/04/18 111351

-

Strömförsörjningsspänningar i elektronik: Betydelsen av VCC, VDD, VEE, VSS och GND

på 0400/04/18 83768

-

RJ45 -anslutningsguide: Pinout, ledningar, kabeltyper och användningar

på 1970/01/1 79565

-

Den ultimata guiden för trådfärgkoder i moderna elektriska system

Hur våra elektriska system använder färger är inte bara för utseende.Varje trådfärg indikerar nu en specifik funktion, vilket gör det lättare att identifiera och hantera elektriska komponenter korr...på 1970/01/1 66960

-

Purge Valve Guide: Funktion, symtom, testning och ersättning för optimal motorprestanda

Purge -ventilen är en viktig del av bilens system som hjälper till att hålla luften ren genom att hantera bränsleångor innan de kan fly in i atmosfären.Detta hjälper inte bara miljön genom att mins...på 1970/01/1 63100

-

Kvalitet (Q) Faktor: Ekvationer och applikationer

Kvalitetsfaktorn, eller 'Q', är viktig när man kontrollerar hur väl induktorer och resonatorer arbetar i elektroniska system som använder radiofrekvenser (RF).'Q' mäter hur väl en krets minimerar e...på 1970/01/1 63040

-

Uppnå toppprestanda med den maximala kraftöverföringssatsen

Den maximala kraftöverföringssatsen förklarar hur energi från en källa, till exempel ett batteri eller generator, flyter till en ansluten belastning.Det visar det exakta tillståndet där lasten får ...på 1970/01/1 54097

-

A23 -batterispecifikationer och kompatibilitet

A23-batteriet är ett litet, cylinderformat batteri med högspänning.Även kallad 23A, 23AE eller MN21, den körs vid 12 volt och mycket högre än AA- eller AAA -batterier.Dess speciella design...på 1970/01/1 52184