XCV200-6FG456C FPGA: Funktioner, specifikationer, programmering och applikationer

XCV200-6FG456C är en kraftfull FPGA (fältprogrammerbar grindarray) från AMD Xilinx Virtex®-serien.Den här guiden förklarar dess funktioner, PIN -layout, programmeringssteg och användningar.Med hög bearbetningskraft, flexibla designalternativ och stark input/utgång (I/O) -funktioner hjälper denna FPGA att bygga snabba och pålitliga digitala system.Oavsett om du arbetar med nätverk, kontrollsystem eller anpassad elektronik, kommer den här guiden att hjälpa dig att förstå hur XCV200-6FG456C kan användas i dina projekt.Katalog

Xcv200-6fg456c översikt

De Xcv200-6fg456c är en anmärkningsvärd modell inom AMD Xilinx Virtex® FPGA -familjen, utformad för att tillhandahålla robusta programmerbara logiklösningar för komplexa digitala system.Detta specifika chip omfattar cirka 236 666 systemgrindar och har 1 176 konfigurerbara logikblock (CLB) och 5 292 logikceller.Det inkluderar också 57 344 totala RAM-bitar och stöder 284 I/O-stift, inrymda i ett 456-boll fin-pitch bollnät Array (FBGA) -paket, som mäter 23 mm x 23mm.Denna modell fungerar på en 2,5V nominell spänning, med ett intervall från 2,375V till 2,625V och kan fungera inom ett temperaturområde från 0 ° C till 85 ° C.Den bredare Virtex® -serien tillgodoser en rad applikationer med täthet från 50 000 till över 1 miljon systemgrindar och systemklockfrekvens på upp till 200 MHz.Det stöder många I/O -standarder inklusive LVTTL, LVCMO och PCI, bland andra.Funktioner som fördröjningslåsta slingor (DLL), konfigurerbara logikblock med inbäddat minne och dedikerad bärlogik för aritmetiska operationer förbättrar dess funktionalitet.Tillverkad med en 0,22 um 5-lagers metallprocess, garanterar Virtex®-familjen prestanda och tillförlitlighet.

Om du vill integrera toppnivå FPGA-teknik i dina produkter eller system är det ett smart drag att köpa XCV200-6FG456C i bulk med oss.Det uppfyller branschstandarder och håller dig före framtida teknikbehov.

XCV200-6FG456C-funktioner

• Systemgrindar: XCV200-6FG456C erbjuder cirka 236 666 systemgrindar.Detta höga grindantal möjliggör implementering av komplexa integrerade digitala logikkretsar på ett enda chip, vilket förbättrar både prestanda och mångsidighet i en rad applikationer.

• Logikresurser: Det inkluderar 1 176 konfigurerbara logikblock (CLB) och 5 292 logikceller.Dessa resurser är bra för att utforma flexibla och skalbara digitala kretsar.CLB: er kan programmeras för att utföra ett brett utbud av logiska funktioner, medan det stora antalet logikceller möjliggör hantering av omfattande logikoperationer och processer.

• Minne: Enheten ger 57 344 bitar av RAM, fördelade mellan dess logikblock.Denna inbäddade RAM används för applikationer som kräver snabb och effektiv datalagring och återhämtning, vilket stödjer höghastighetsdatager som är integrerad i moderna digitala system.

• I/O -kapacitet: Med 284 ingångs-/utgångsstift underlättar XCV200-6FG456C omfattande gränssnittsfunktioner.Dessa I/O -stift stöder olika signalstandarder och gör det möjligt för FPGA att kommunicera effektivt med andra komponenter i ett system, såsom minnesenheter, processorer och kringutrustning.

• Spännings- och temperaturområde: Arbetar med en nominell spänning på 2,5V, med ett acceptabelt intervall från 2,375V till 2.625V, är denna FPGA utformad för låg effektförbrukning samtidigt som man bibehåller robust prestanda.Det kan fungera inom ett korsningstemperaturområde från 0 ° C till 85 ° C, vilket säkerställer tillförlitlighet under olika miljöförhållanden.

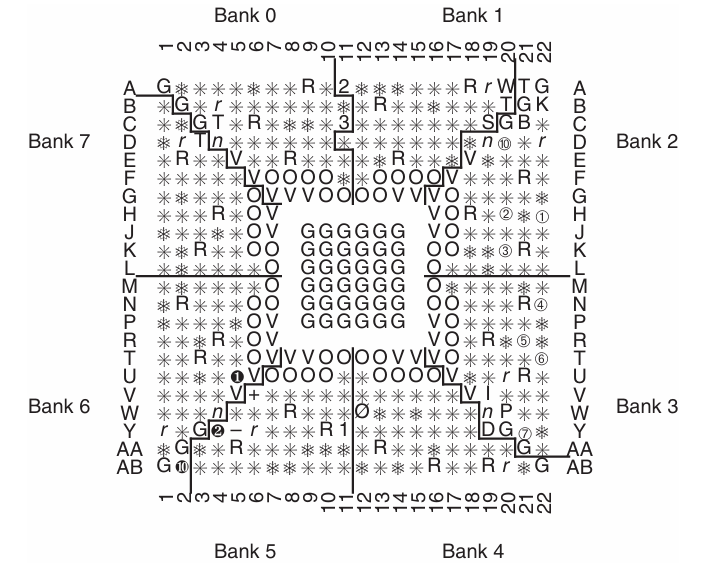

XCV200-6FG456C PIN-funktionsdiagram

De XCV200-6FG456C PIN-funktionsdiagram är en strukturerad representation av FPGA: s stiftuppdrag, kategoriserade i olika banker (Bank 0 till bank 7).Varje bankgrupper stift baserat på deras funktion och fysiska placering på FPGA -paketet.Numrerings- och märkningssystemet följer ett rutmönster där rader betecknas med bokstäver (a, b, c, etc.) och kolumner efter siffror (1, 2, 3, etc.), vilket underlättar snabb identifiering av specifika stift.Dessa banker motsvarar olika ingångs-/utgångsfunktioner, kraft, mark och dedikerad signalrutning.Stifter tilldelas olika funktionella grupperingar, inklusive I/O (GPIO) i allmänhet, ofta märkt som "G" (allmän ingång/utgång), "V" (spänningsförsörjning) och "O" (utgång).Kraft- och markstift markeras tydligt, vilket säkerställer stabil FPGA -drift.Speciella stift som klockingångar, återställningar och styrsignaler identifieras med symboler som "R" eller "T."Vissa stift serverar också dedikerade kommunikationsroller, inklusive JTAG-konfiguration och höghastighetsklockning, för programmering och felsökning.

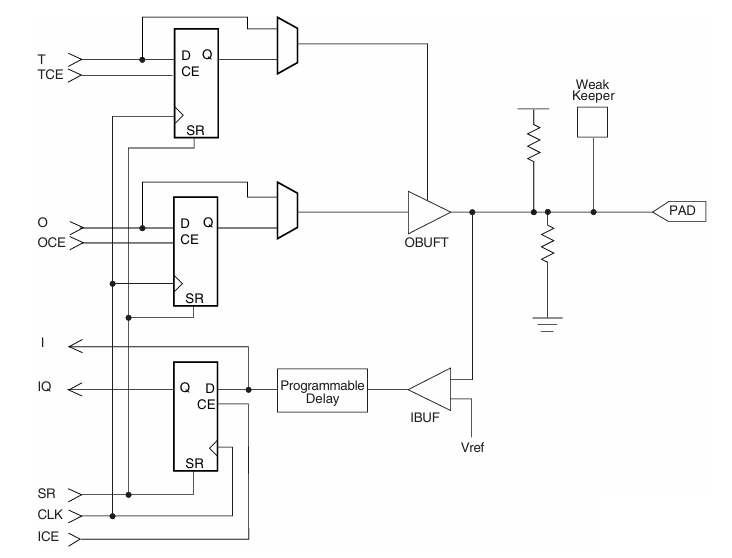

XCV200-6FG456C blockdiagram

Ingångs-/utgångsblock

Diagrammet representerar Input/Output Block (IOB) Struktur av XCV200-6FG456C FPGA, som är medlem i Xilinx Virtex-familjen.Diagrammet visar nyckelelement som är involverade i ingångs- och utgångsoperationer, vilket belyser dataflödes- och kontrollmekanismerna.I kärnan i diagrammet används tre D-flip-flops för att registrera signaler för inmatning, utgång och tri-state-kontroll.Utgångsregistret styrs av OCE (utgångsklockan Enable) -signalen, som bestämmer när utgångsdata är låst.På liknande sätt styrs Tri-State Register av TCE (Tri-State Clock Enable), vilket möjliggör eller inaktiverar utgångsbufferten.Inmatningsregistret fångar inkommande data och tillämpar en programmerbar fördröjning innan den överför den till den interna FPGA -logiken genom IBUF (ingångsbuffert).Obuft (Tri-State utgångsbuffert) säkerställer att FPGA antingen kan köra en signal på dynan (I/O-stiftet) eller placera den i ett högtimpedansläge, beroende på kontrolllogiken.En svag keeper -krets ingår på dynan för att upprätthålla det senaste kända logikstillståndet när ingen aktiv förare är närvarande, vilket förhindrar oavsiktliga flytande förhållanden.Referensspänningen (VREF) används för vissa ingångsstandarder, såsom SSTL eller HSTL, som kräver exakta spänningsnivåer för korrekt drift.Sammantaget tillåter denna IOB-struktur FPGA att hantera höghastighetsdataöverföring, stödja olika I/O-standarder och ge flexibel kontroll över signaltid och integritet.

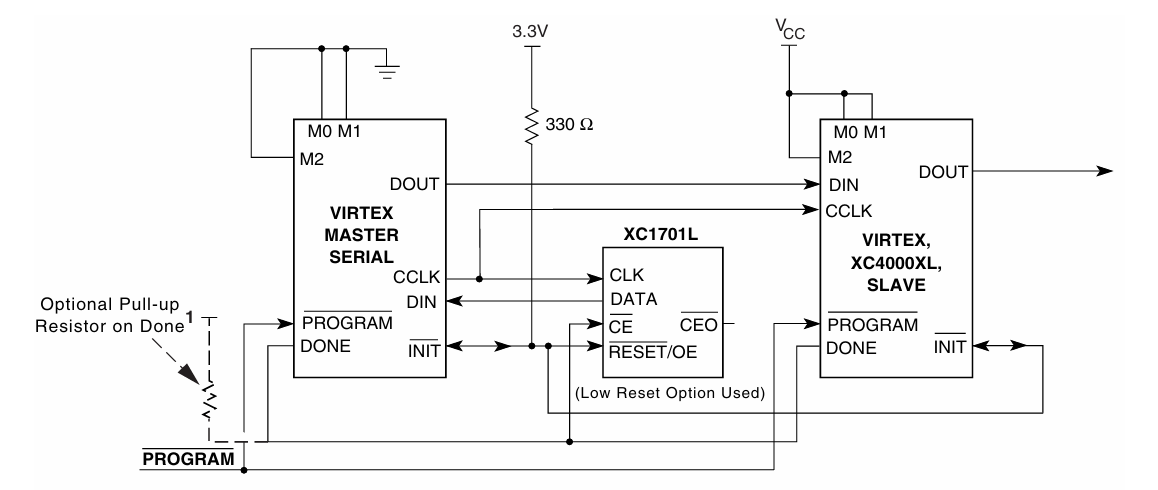

Master/Slave Serial Mode

De Master/Slave Serial Mode Blockdiagram illustrerar konfigurationsprocessen för en Virtex FPGA, särskilt XCV200-6FG456C, när den programmeras i en Daisy-Chain-konfiguration med en seriell EEPROM (XC1701L).I denna installation fungerar en Virtex -enhet som master och kontrollerar konfigurationsklockan (CCLK) och seriellt överför konfigurationsdata till ytterligare slav FPGA i kedjan.Master FPGA initierar konfigurationsprocessen genom att hävda programsignalen och återställa alla enheter i kedjan.När initialiseringen är klar indikerar init -signalen beredskap, och konfigurationsdata flyter från seriell EEPROM (XC1701L) till DIN (data in) -stiftet i Master FPGA.Mästaren FPGA läser data från EEPROM och vidarebefordrar dem genom dout (data ut) till efterföljande slav FPGA: er, synkroniserar dataöverföring med CCLK -signalen.Den gjorda signalen används för att indikera framgångsrik konfiguration, med ett valfritt pull-up-motstånd som säkerställer ett stabilt högt tillstånd när konfigurationen är klar.XC1701L EEPROM styrs av Master FPGA med CLK, data, CE (CHIP Aktivera) och återställning/OE (utgångsaktivering) -signaler, vilket säkerställer att de lagrade konfigurationsdata är korrekt hämtade.Denna konfigurationsmetod är effektiv för att programmera flera FPGA: er med hjälp av en enda EEPROM, minska extern ledningskomplexitet och säkerställa att alla enheter får synkroniserade konfigurationsdata.

XCV200-6FG456C-specifikationer

|

Typ |

Parameter |

|

Tillverkare |

AMD XILINX

|

|

Serie |

Virtex® |

|

Förpackning |

Bricka |

|

Delstatus |

Föråldrad |

|

Antal laboratorier/clbs |

1176 |

|

Antal logikelement/celler |

5292 |

|

Totala RAM -bitar |

57344 |

|

Antal I/O |

284 |

|

Antal grindar |

236666 |

|

Spänning - försörjning |

2.375V ~ 2.625V |

|

Monteringstyp |

Ytfäste |

|

Driftstemperatur |

0 ° C ~ 85 ° C (TJ) |

|

Förpackning / fodral |

456-bbga |

|

Leverantörspaket |

456-FBGA (23x23) |

|

Basproduktnummer |

Xcv200 |

XCV200-6FG456C-applikationer

Telekommunikation och nätverk

XCV200-6FG456C utmärker sig i telekommunikations- och nätverksapplikationer på grund av dess förmåga att hantera höghastighetsdataöverföringar och komplexa signalbehandlingsuppgifter.Dess höga grindantal och robusta I/O -kapacitet gör det möjligt att stödja funktioner som paketbehandling, signalmodulering/demodulering och felkorrigeringsprotokoll.

Digital signalbehandling (DSP)

PPGA är idealisk för DSP -applikationer och kan utföra snabba och komplexa matematiska beräkningar som krävs inom ljud- och videobearbetningsteknologier.Oavsett om det är för multimediasystem, röstigenkänning eller strömningstjänster, stöder XCV200-6FG456C: s kraftfulla bearbetningsfunktioner och inbäddat minne effektiv och högkvalitativ signalbehandling.

Industrikontrollsystem

I den industriella automatiseringen tillhandahåller XCV200-6FG456C den nödvändiga prestanda för att hantera styrsystem och automatiseringsnätverk.Dess förmåga att utföra flera kontrolluppgifter samtidigt och samtidigt säkerställa responstider gör det lämpligt för applikationer inom processkontroll, robotik och maskinvision.

Medicinska instrument

FPGA: s precision och hastighet är bra i medicinsk avbildning och diagnostisk utrustning, där den hjälper till att bearbeta komplexa algoritmer för avbildningsapplikationer som MRI, ultraljud och CT -skanningar.XCV200-6FG456C: s kapacitet säkerställer att den kan hantera hög dataöverföring och intrikata behandlingar som krävs i modern medicinsk teknik.

XCV200-6FG456C Liknande delar

XCV200-6FG456C-programmeringssteg

Programmeringssteg för XCV200-6FG456C:

1. Designpost

Den inledande fasen av FPGA -programmering innebär att du definierar den digitala logiken och funktionaliteten i ditt system.Detta kan göras med hjälp av hårdvarubeskrivning Languages (HDL) som VHDL eller Verilog, där du skriver kod som anger hur FPGA bearbetar data och interagerar med annan hårdvara.Schematiska inmatningsverktyg som finns tillgängliga i FPGA -designprogramvara som Xilinx ISE eller Vivado kan användas.Denna metod innebär att skapa en visuell representation av logiken genom att dra och släppa komponenter, som vissa tycker är mer intuitiva än att skriva kod.

2. Syntes

När designen är klar är nästa steg syntes, där ett verktyg som Xilinxs XST (Xilinx Synthesis Technology) förvandlar din HDL -kod eller schematisk design till en netlist.Den här netlistan beskriver kretsen i termer av generiska digitala komponenter, till exempel logikgrindar och register.Syntesprocessen innebär också att optimera designen för att uppfylla prestandakraven och minimera resursanvändningen för effektiv FPGA -drift.

3. Implementering

Implementeringsprocessen börjar med översättning och kombinerar din design med begränsningsfiler som anger parametrar som klockfrekvenser och PIN -tilldelningar.Efter översättning tilldelar kartläggningssteget elementen i din netlista till specifika fysiska resurser på FPGA, som uppslagstabeller (LUTS) och flip-flops.Placerings- och routingfasen bestämmer sedan de fysiska platserna för varje komponent inom FPGA: s arkitektur och fastställer sambanden mellan dem genom programmerbara sammankopplingsresurser.Detta steg är utmärkt för att uppnå önskade prestandametriker, inklusive klockfrekvenser.

4. Bitstream -generation

Efter framgångsrik placering och routing genererar verktyget en bitström, en binär konfigurationsfil som innehåller all programmeringsinformation för FPGA.Det rekommenderas ofta att simulera den slutliga designen efter placering för att säkerställa att bitströmmen kommer att bete sig som förväntat under förhållanden.Detta verifieringssteg hjälper till att undvika potentiella problem under den faktiska driften.

5. Konfiguration

Det sista steget innebär att ladda bitströmmen i FPGA med olika konfigurationsmetoder.Slave-seriellt läge, ett enkelt och kostnadseffektivt alternativ, konfigurerar FPGA via en extern master-enhet som skickar data seriellt.I master-seriellt läge läser FPGA autonomt bitströmmen från en bifogad seriell prom.För höghastighetskonfigurationer tillåter SelectMAP-läge en extern mikroprocessor att ladda data snabbt i FPGA.Dessutom används JTAG-läge inte bara för programmering utan också för testning och felsökning, med ett standardgränssnitt för programmering i systemet och gränsskanningstest.

XCV200-6FG456C fördelar

Prestanda

Xilinx Virtex-serien, till vilken XCV200-6FG456C tillhör, är optimerad för höghastighetsprestanda och erbjuder systemklockfrekvenser på upp till 200 MHz.Detta gör det väl lämpat för applikationer som kräver snabb databehandling, vilket säkerställer effektiv hantering av komplexa algoritmer och höghastighetsoperationer som telekommunikation, bearbetning och multimedia.

I/O -standardstöd

Denna FPGA stöder ett brett utbud av ingångs-/utgångsstandarder, inklusive LVTTL, LVCMOS, PCI, GTL, HSTL, SSTL, CTT och AGP.Sådana omfattande I/O-standarder stöder möjliggör XCV200-6FG456C att integreras sömlöst med olika systemkomponenter, vilket förbättrar dess användbarhet över olika digitala ekosystem.Denna flexibilitet gör det möjligt att anpassa FPGA till olika gränssnittsförhållanden utan systemändringar.

Klockstyrelse

XCV200-6FG456C innehåller flera fördröjningslåsta slingor (DLL) för klockdistribution och hantering inom systemet.Dessa DLL: er hjälper till att förbättra systemtiming och tillförlitlighet genom att tillhandahålla exakta klocksignaler som är nödvändiga för synkrona operationer.Denna funktion är viktig för att minska systemfel och förbättra den totala prestandan, särskilt i komplexa mönster som kräver korrekt tidpunkt och synkronisering.

Designflexibilitet

Med 1 176 konfigurerbara logikblock och 5 292 logikceller erbjuder XCV200-6FG456C betydande logikresurser med förmågan att implementera ett brett utbud av funktionaliteter.Från enkel limlogik till intrikata digitala system stöder denna FPGA komplexa designkrav, vilket gör den idealisk för applikationer inom anpassad dator, digital signalbehandling och prototyp.

Snabb prototyp

FPGA: er som XCV200-6FG456C är kända för sin förmåga att stödja snabb prototyp.Den här enheten möjliggör snabba design-iterationer och kan konfigureras in-fältet, vilket är en fördel för utvecklingscykler eftersom den minskar tid till marknad.Den anpassar också effektivt till förändrade krav eller uppdateringar i projektspecifikationer, vilket säkerställer att de slutliga produkterna är uppdaterade med de senaste tekniska standarderna.

Integrationsförmåga

Integrationsfunktionerna för XCV200-6FG456C underlättar konsolidering av flera diskreta komponenter till ett enda chip.Denna integration kan leda till minskad systemkomplexitet, lägre kraftförbrukning och kostnadsbesparingar.Genom att minimera antalet separata komponenter förenklar denna FPGA designprocesser och förbättrar tillförlitligheten och kompaktheten i det övergripande systemet.

XCV200-6FG456C förpackningsdimensioner

XCV200-6FG456C är en fältprogrammerbar grindarray (FPGA) från AMD: s Virtex®-serie, inrymt i ett 456-boll Fine-Pitch Ball Grid Array (FBGA) -paket.

• Pakettyp: 456-fbga

• Paketstorlek: 23 mm x 23 mm

• Bollplan: 1,0 mm

XCV200-6FG456C tillverkare

XCV200-6FG456C är en fältprogrammerbar grindarray (FPGA) som ursprungligen utvecklats av Xilinx, ett företag känt för sina högpresterande programmerbara logikenheter.Efter Xilinx förvärv av Amd, XCV200-6FG456C är nu associerad med AMD som dess nuvarande tillverkare.Men denna FPGA -modell är föråldrad och inte längre i produktion.AMD fortsätter att stödja nyare FPGA -arkitekturer med förbättrad prestanda, krafteffektivitet och utökad livslängd, vilket gör moderna alternativ att föredra för nya mönster.

Slutsats

XCV200-6FG456C är en mångsidig och höghastighets FPGA, användbar för många teknikapplikationer.Även om det inte längre görs, är det fortfarande ett bra val för äldre system som behöver tillförlitlig prestanda.Den här guiden har täckt sin design, programmeringssteg och praktiska användningar, vilket gör det lättare att förstå hur den fungerar och hur den kan användas.När nyare FPGA blir tillgänglig kan du använda denna kunskap för att välja rätt FPGA för dina behov och förbättra digitala mönster.

Datablad pdf

XCV200-6FG456C Datablad:

Om oss

ALLELCO LIMITED

Läs mer

Snabb förfrågan

Skicka en förfrågan, vi svarar omedelbart.

Vanliga frågor [FAQ]

1. Vad är kraftförbrukningen för XCV200-6FG456C?

XCV200-6FG456C fungerar vid 2,5V, med ett spänningsområde på 2,375V till 2,625V.Strömförbrukning beror på logikutnyttjande och klockfrekvens, men som en äldre FPGA kan det vara mindre effekteffektivt än nyare Xilinx-enheter.Korrekt krafthantering och värmeavledning bör övervägas.

2. Hur jämför XCV200-6FG456C med XCV200-6FG256C?

XCV200-6FG456C har ett större paket (456-boll FBGA) jämfört med XCV200-6FG256C (256-boll FBGA), vilket erbjuder mer I/O-stift (284 mot 172) och potentiellt bättre prestanda för applikationer som kräver omfattande interfacing.Om din design förlitar sig på mer I/O-funktioner är XCV200-6FG456C det bättre valet.

3. Kan jag omprogrammera XCV200-6FG456C flera gånger?

Ja, XCV200-6FG456C är en SRAM-baserad FPGA, vilket innebär att den kan omprogrammeras ett obegränsat antal gånger så länge som ström levereras.Du kommer dock att behöva externt icke-flyktigt minne (EEPROM eller Flash) för att behålla bitströmmen efter en kraftcykel.

4. Stödjer XCV200-6FG456C höghastighetsseriekommunikation?

XCV200-6FG456C stöder flera I/O-standarder som LVTTL, LVCMOS, PCI, GTL, HSTL och SSTL, men det har inte inbyggda höghastighets Serdes (Serializer/Deserializer) eller sändare som moderna FPGA.För applikationer som kräver höghastighetsserielänkar (t.ex. PCIe, Gigabit Ethernet eller HDMI), överväg nyare FPGA-modeller.

5. Hur jämför XCV200-6FG456C med nyare FPGA-modeller?

XCV200-6FG456C tillhör en äldre generation av FPGA.Jämfört med moderna Virtex FPGA: er har det ett lägre grindantal, långsammare klockhastigheter och begränsad effekteffektivitet.Nyare modeller erbjuder högre logikdensitet, mer inbäddat minne, avancerade DSP -block och lägre strömförbrukning, vilket gör dem bättre för moderna applikationer.

AD73322ar pinout, funktioner och tekniska detaljer förklarade

på 2025/03/21

EP20K100EFC324-1X FPGA: Funktioner, specifikationer, applikationer och programmeringsguide

på 2025/03/20

Populära inlägg

-

Komplexa instruktionsuppsättningsdatorer: Hur de ändrade datoranvändning?

på 8000/04/17 147721

-

USB-C-pinout och funktioner

på 2000/04/17 111783

-

Använda Xilinx Unified Simulation Primitives: En omfattande guide till FPGA -design och simulering

på 1600/04/17 111328

-

Strömförsörjningsspänningar i elektronik: Betydelsen av VCC, VDD, VEE, VSS och GND

på 0400/04/17 83649

-

RJ45 -anslutningsguide: Pinout, ledningar, kabeltyper och användningar

på 1970/01/1 79354

-

Den ultimata guiden för trådfärgkoder i moderna elektriska system

Hur våra elektriska system använder färger är inte bara för utseende.Varje trådfärg indikerar nu en specifik funktion, vilket gör det lättare att identifiera och hantera elektriska komponenter korr...på 1970/01/1 66806

-

Kvalitet (Q) Faktor: Ekvationer och applikationer

Kvalitetsfaktorn, eller 'Q', är viktig när man kontrollerar hur väl induktorer och resonatorer arbetar i elektroniska system som använder radiofrekvenser (RF).'Q' mäter hur väl en krets minimerar e...på 1970/01/1 62967

-

Purge Valve Guide: Funktion, symtom, testning och ersättning för optimal motorprestanda

Purge -ventilen är en viktig del av bilens system som hjälper till att hålla luften ren genom att hantera bränsleångor innan de kan fly in i atmosfären.Detta hjälper inte bara miljön genom att mins...på 1970/01/1 62859

-

Uppnå toppprestanda med den maximala kraftöverföringssatsen

Den maximala kraftöverföringssatsen förklarar hur energi från en källa, till exempel ett batteri eller generator, flyter till en ansluten belastning.Det visar det exakta tillståndet där lasten får ...på 1970/01/1 54049

-

A23 -batterispecifikationer och kompatibilitet

A23-batteriet är ett litet, cylinderformat batteri med högspänning.Även kallad 23A, 23AE eller MN21, den körs vid 12 volt och mycket högre än AA- eller AAA -batterier.Dess speciella design...på 1970/01/1 52032