EPF6016ATC144-2N FPGA: Funktioner, programmering, applikationer och alternativ

Den här guiden handlar om EPF6016ATC144-2N, en typ av chip som kallas en FPGA.Det används i digitala system som måste vara flexibla och enkla att uppdatera.Guiden förklarar vad chipet gör, hur det fungerar, dess huvuddelar och funktioner, hur man använder och programmerar den, var den kan användas och varför det fortfarande är ett bra val idag.Katalog

Vad är EPF6016ATC144-2N?

De EPF6016ATC144-2N är medlem i Flex 6000 FPGA -familjen utvecklad av Altera, nu en del av Intel.Denna enhet byggd på SRAM-baserad omprogrammerbar logik och är konstruerad för flexibilitet i digitala logiska applikationer i mitten av densiteten.Den utnyttjar OptiFlex-arkitekturen, som kombinerar logiska arrayblock (LAB) och en höghastighets-interconnect-matris för att leverera effektivt resursanvändning och snabb signalrutning.EPF6016ATC144-2N stöder rekonfigurering i systemet, vilket gör den idealisk för mönster som kräver uppdateringar eller ändringar efter utplacering.Som en del av Flex 6000-serien erbjuder den en kostnadseffektiv lösning för att ersätta traditionella grinduppsättningar samtidigt som man förenklar utvecklingscykeln.

Letar du efter EPF6016ATC144-2N?Kontakta oss för att kontrollera nuvarande lager, ledtid och prissättning.

EPF6016ATC144-2N CAD-modeller

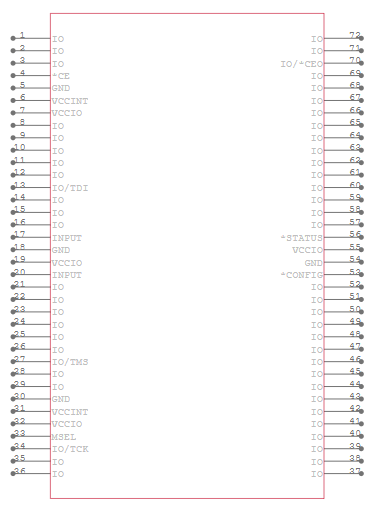

EPF6016ATC144-2N Symbol

EPF6016ATC144-2N FOTPRINT

EPF6016ATC144-2N 3D-modell

EPF6016ATC144-2N-funktioner

• Logikkapacitet

EPF6016ATC144-2N erbjuder cirka 16 000 systemgrindar, implementerade med hjälp av 1 320 logikelement (LES) över 132 logikuppsättningsblock (Labs).Detta ger måttlig komplexitet som är lämplig för Mid-Range FPGA-applikationer.

• I/O -stift

Det stöder upp till 117 användarkonfigurerbara I/O-stift.Dessa stift möjliggör flexibel anslutning till olika systemkomponenter och externa enheter.

• Kärnspänning

Kärnan fungerar vid 3,3V med ett funktionellt intervall från 3,0V till 3,6V. Detta möjliggör kompatibilitet med standard digitala system med låg spänning.

• I/O -spänning

Dess multivolt I/O -funktion stöder gränssnitt med enheter med 3,3V eller 2,5V nivåer.Detta förenklar integrationen i miljöer med blandade spänningar.

• Driftstemperatur

Standardtemperaturområdet för driftskorsning är 0 ° C till +85 ° C.Detta stöder typiska kommersiella och industriella miljöer.

• Leverantör

Det drar ungefär 5 mA under normal drift och mindre än 0,5 mA i standby -läge.Detta hjälper till att spara kraft i energimedvetna mönster.

• Klockhastighet (hastighetskvalitet –2n)

Med en –2 -hastighetsgrad uppnår den interna logiska frekvenser upp till cirka 166 MHz.Detta möjliggör snabb beräkning vid signalbehandling eller kontrolllogik.

• Arkitektur

Baserat på Alteras Optiflex-arkitektur använder den LUT-baserad logik med dedikerade routingresurser.Denna arkitektur erbjuder hög logisk densitet och effektiv prestanda.

• FastTrack Interconnect

FastTrack Routing Grid möjliggör signalvägar med låg latens och stöder höghastighetsdataöverföringar över logikblock.Detta bidrar till konsekvent timing och prestanda.

• Rekonfigurering

Den använder SRAM-baserad logikkonfiguration, vilket gör att FPGA kan omprogrammeras i systemet.Detta stöder designuppdateringar eller dynamisk anpassning av hårdvara utan borttagning.

• JTAG -gränsscanning

Enheten inkluderar IEEE 1149.1-kompatibel JTAG-gränsskanningslogik.Detta underlättar felsökning och testbarhet i systemet för styrelser och sammankopplingar.

• Hot sockelying stöd

Det kan sättas in eller tas bort när du drivs i 3.3V -system.Den här funktionen är användbar i modulära eller användbara hårdvaruplattformar.

• Funktionell testning

Varje enhet testas fullt funktionellt före leverans.Detta säkerställer kvalitet och eliminerar behovet av användardefinierade testvektorer under utvecklingen.

• PCI -kompatibilitet

Enheten är kompatibel med PCI Local Bus Revision 2.2 för 5V -drift.Detta gör att den kan användas i äldre PCI-baserade inbäddade system.

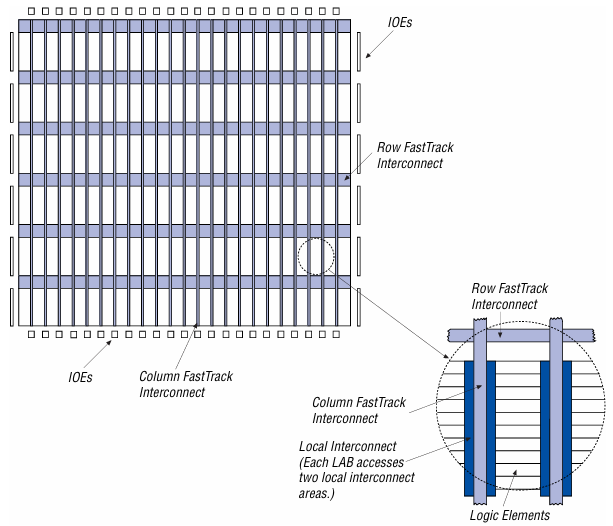

Optiflex arkitekturblockdiagram

Diagrammet visar hur de inre delarna av FPGA är organiserade och anslutna.I mitten finns logiska arrayblock (labb), dessa är de viktigaste byggnadsenheterna i chipet.Varje laboratorium innehåller flera logikelement (LES) som utför de grundläggande digitala operationerna, såsom logikgrindar och flip-flops.Labs är anslutna med en lokal sammankoppling, som gör det möjligt för logiken i varje block att fungera effektivt.För bredare kommunikation över chipet länkar laboratorierna till rad- och kolumnfasttrack -sammankopplingar, snabba signalvägar som låter data röra sig snabbt från en del av chipet till en annan med låg fördröjning.Runt de yttre kanterna på diagrammet finns ingångs-/utgångselementen (IOE).Dessa ansluter FPGA: s interna logik till externa enheter genom att konvertera mellan chipets logiknivåer och spänningsnivåerna som används av annan hårdvara.Denna layout, med sina modulära block och höghastighets routingvägar, återspeglar flexibiliteten och prestandafokuset för OptiFlex-arkitekturen.

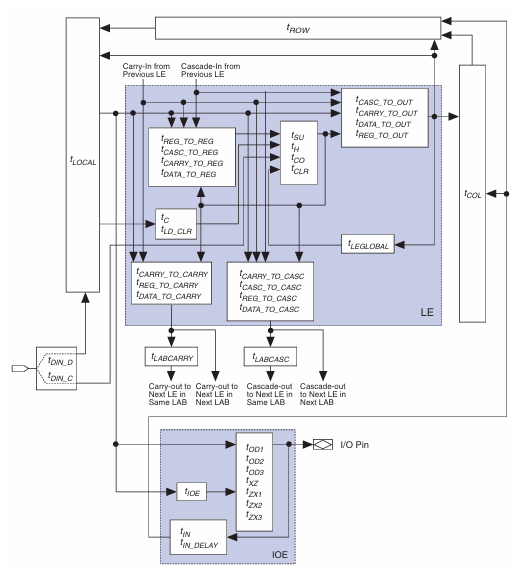

Flex 6000 tidsmodell

Flex 6000 -tidsmodellen visar hur signaler rör sig och försenas när de reser genom FPGA.I mitten av modellen finns logikelement (LES), som bearbetar data och styrsignaler med specifik timing.Varje Le ansluter till tidsvägar som T_DATA_TO_REG och T_REG_TO_OUT, som definierar hur lång tid det tar för signaler att komma in, bearbetas och lämna logiken.

Bredvid LES finns speciella vägar som kallas Lab Carry och Lab Cascade.Dessa gör det möjligt för signaler att röra sig horisontellt mellan logikelement i samma block, vilket stödjer snabba operationer som tillägg och jämförelser.Dessa vägar har också sina egna tidsvärden, till exempel T_CARRY_TO_REG och T_CASC_TO_OUT, för att mäta förseningar under dessa operationer.

Längst ner i diagrammet hanterar ingångs-/utgångselementen (IOE) signaler som går in och ut ur chipet.De inkluderar fördröjningspunkter som T_IN_DELAY, som står för variationer när de tar emot data från externa enheter.

Modellen inkluderar också routingvägar på olika nivåer (T_LOCAL, T_ROW, T_COL och T_GLOBAL) som var och en representerar hur långt en signal reser och hur mycket tid det tar.Dessa vägar hjälper till att förstå och hantera förseningar över olika delar av chipet, vilket gör det lättare att uppfylla prestandamål.

EPF6016ATC144-2N-specifikationer

|

Typ |

Parameter |

|

Tillverkare |

Altera/intel |

|

Serie |

Flex 6000 |

|

Förpackning |

Bricka |

|

Delstatus |

Föråldrad |

|

Antal laboratorier/clbs |

132 |

|

Antal logikelement/celler |

1320 |

|

Antal I/O |

117 |

|

Antal grindar |

16000 |

|

Spänning - försörjning |

3V ~ 3,6V |

|

Monteringstyp |

Ytfäste |

|

Driftstemperatur |

0 ° C ~ 85 ° C (TJ) |

|

Förpackning / fodral |

144-LQFP |

|

Leverantörspaket |

144-TQFP (20x20) |

|

Basproduktnummer |

EPF6016 |

EPF6016ATC144-2N-applikationer

1. Digital Signal Processing (DSP) -uppgifter

Med 1 320 logikelement och snabba sammankoppling stöder EPF6016ATC144-2N implementering av små till mellanklass-digitala signalbehandlingsfunktioner.Det kan användas för att skapa anpassade FIR -filter, FFT -kärnor eller parallell aritmetisk logik för signalomvandling.Även om den saknar dedikerade DSP-block eller inbäddade multiplikatorer, kan dess allmänna logik hantera repetitiva multipliceringsoperationer som är lämpliga för inbäddad ljudbehandling, sensordatafiltrering och vågformformning i kontroll- eller kommunikationssystem.

2. Inbäddad kontroll och industriell automatisering

Enheten är väl lämpad för inbäddade kontrollapplikationer i industriella miljöer.Dess förmåga att gränssnitt med blandad spänning I/O (2,5 V och 3,3 V), dess stabila drift under standard kommersiella temperaturer (0–85 ° C) och stöd för hot-hocking gör det tillförlitligt för integration i programmerbara logikstyrenheter (PLC), motorstyrenheter, instrumenteringsgränssnitt och allmänna automatiseringsutrustning.Omkonfigurerbarheten möjliggör långsiktig produktflexibilitet, där logik kan uppdateras utan att ersätta hårdvara.

3. Kommunikationsprotokollbryggning och gränssnittslogik

Tack vare sitt multivolt I/O-stöd och effektiva routingnätverk kan EPF6016ATC144-2N användas för att implementera anpassade kommunikationsgränssnitt och protokollomvandlare.Det kan bygga Uarts, SPI -kontroller eller parallella bussöversättare för att möjliggöra interaktion mellan ojämförliga digitala system.Dess måttliga I/O-räkning (117 GPIO) och intern klockhantering stöder också tidskänslig signalering, vilket gör det lämpligt för nätverksutrustning, äldre bussemulering eller som ett limlogikelement i större datakommunikationssystem.

4. Test, felsökning och validering på styrelsenivå

Med inbyggd JTAG-gränsskanning (IEEE 1149.1-kompatibel) stöder EPF6016ATC144-2N avancerad tester på styrelsenivå utan att kräva externa logiska prober eller påträngande diagnostik.Den kan verifiera I/O-anslutning, upptäcka öppna eller kortslutna kretsar och utföra kontroller i systemet under produktions- eller fältunderhåll.Denna funktion är användbar i komplexa flerskikts -PCB eller i system där traditionell åtkomst till testpunkter är begränsad eller opraktisk.

EPF6016ATC144-2N Liknande delar

|

Drag |

EPF6016ATC100-1 |

EPF6016ATC100-3N |

EPF6016ATC144-3N |

|

Tillverkare |

Alta |

Intel (Altera Legacy) |

Intel (Altera Legacy) |

|

Familj |

Flex 6000 |

Flex 6000 |

Flex 6000 |

|

Logikelement (LES) |

1,320 |

1,320 |

1,320 |

|

Gate Count (ca.) |

16 000 |

16 000 |

16 000 |

|

Paket |

100-stifts TQFP |

100-stifts TQFP |

144-stift TQFP |

|

Användare I/O -stift |

81 |

81 |

117 |

|

Hastighetsgrad |

-1 (standard) |

-3n (hög hastighet) |

-3n (hög hastighet) |

|

Max klockfrekvens |

Lägre (vanligtvis ~ 100 MHz) |

Högre (upp till ~ 166 MHz) |

Högre (upp till ~ 166 MHz) |

|

Konfigurationstyp |

SRAM-baserad |

SRAM-baserad |

SRAM-baserad |

|

Strömförsörjningsspänning |

3,3 v |

3,3 v |

3,3 v |

|

Hethöjd |

Ja |

Ja |

Ja |

|

JTAG/gränsskanning |

Ja |

Ja |

Ja |

|

Ansökningar |

Grundläggande logik, kompakta mönster |

Snabbare kontrolllogik, kompakt |

Högpresterande system, mer I/O |

|

Tillgänglighet |

Föråldrad |

Föråldrad |

Föråldrad |

EPF6016ATC144-2N-programmeringssteg

1. Välj konfigurationsläge

EPF6016ATC144-2N stöder SRAM-baserad konfiguration, vilket innebär att den kräver programmering på varje power-up.Enheten möjliggör flera konfigurationsscheman, oftast passiva serie (PS) och passiva parallella asynkron (PPA).Konfigurationsläget bestäms av hur MSEL -stiftet är anslutet.Till exempel, när MSEL är bunden, förväntar sig enheten att data skickas seriellt via extern EEPROM (som EPC1) eller en nedladdningskabel.Att välja rätt konfigurationsmetod beror på systemdesignen, EEPROM-baserad för automatisk uppstart eller kabelbaserad för prototypning och testning.

2. Kompilera FPGA -designen och generera en programmeringsfil

För att programmera FPGA måste du först skapa din hårdvarudesign med Intels Quartus eller Legacy Max+Plus II Design Software.Efter kompilering genererar verktyget en SOF (SRAM -objektfil) som representerar den konfigurerade logiken.Denna SOF måste sedan konverteras till ett format som är kompatibelt med din valda konfigurationsmetod:

• .rbf eller .poF för EEPROM -enheter (t.ex. EPC1).

• .TTF eller .HEX för mikrokontroller eller parallellbelastning.

Konverteringen görs med det inbyggda filkonverteringsverktyget i designprogramvaran.Detta steg säkerställer att bitströmmen formateras korrekt för att FPGA ska tolka.

3. Programmera konfigurationsminnet (om du använder EEPROM)

I applikationer där en seriekonfigurationsenhet som en EPC1 används är nästa steg att ladda konfigurationsdata i EEPROM.Detta görs vanligtvis med ett skrivbordsprogrammeringsverktyg (t.ex. Max+Plus II -programmerare eller Quartus -programmerare).Processen innebär att du placerar EEPROM i ett programmeringsuttag eller ansluter den i kretsen, laddar lämplig programmeringsfil (vanligtvis .poF eller .RBF) och initiera programcykeln.När EEPROM har programmerats tillhandahåller EEPROM automatiskt konfigurationsdata till FPGA varje gång systemet drivs upp, vilket eliminerar behovet av manuell omprogrammering.

4. Konfigurera med en nedladdningskabel (passiv serie)

Ett alternativ till EEPROM-baserad start är att använda en nedladdningskabel (som USB-Blaster eller ByteBlaster) för att direkt konfigurera FPGA.I den här metoden ansluter du kabeln till din PC och FPGA: s NConfig, DCLK, data och conf_done -stift.Med hjälp av Quartus -programmeraren initierar du konfigurationsprocessen, som pulserar nconfig låg för att börja.Verktyget skickar sedan konfigurationsdata seriellt via datalinjen, klockad av DCLK.Processen är klar när Conf_Done går högt, vilket indikerar framgångsrik konfiguration och enhetens övergång till användarläge.

5. Konfigurera med en mikrokontroller (passiv serie/parallell)

Om ditt system använder en inbäddad mikrokontroller kan det också fungera som FPGA: s konfigurationsmaster.I denna installation hävdar mikrokontrollern Nconfig låg för att återställa FPGA och flyttar sedan konfigurationsbitströmmen genom data medan de växer DCLK.Tidskraven måste respekteras, datainställningstid före klockan och håll tid därefter är bra för framgångsrik konfiguration.Mikrokontrollern kan övervaka nstatus- och conf_done -stiften för att upptäcka konfigurationsfel eller bekräfta framgångsrik slutförande.Denna metod erbjuder full kontroll över konfigurationsprocessen och stöder dynamiska uppdateringar i fältet.

6. Övervaka konfigurationssignaler

Under konfigurationsprocessen ger FPGA feedback genom statusstift:

• NStatus indikerar feldetektering;Det går lågt om ett fel inträffar (t.ex. CRC -fel eller tidpunktöverskridande).

• Conf_done går högt när alla konfigurationsbitar har laddats och verifieras.

Om NStatus förblir hög och Conf_Done övergår högt i slutet av sekvensen, går enheten automatiskt in i användarläge, där användardefinierad logik blir aktiv.Denna signalövervakning är viktig för att säkerställa att programmeringsprocessen slutförs framgångsrikt.

7. Utför rekonfiguration vid behov

Eftersom EPF6016ATC144-2N är SRAM-baserad kan den när som helst konfigureras genom att växla NCONFIG-stiftet lågt, som återställer enheten och startar om konfigurationscykeln.Denna funktion möjliggör flexibla systemuppdateringar och förändringar under drift utan fysisk ersättning.Möjligheten att konfigurera om medan i krets stöder också redundans, dynamisk funktionsbyte eller korrigera buggar efter utplacering.Detta gör enheten mycket lämplig för applikationer som kräver anpassningsbarhet eller livslängd.

8. Observera tidpunkten och elektriska krav

Programmering av EPF6016ATC144-2N kräver också uppmärksamhet på elektriska och tidsbegränsningar.Konfigurationsklockan (DCLK) måste uppfylla frekvensgränserna (t.ex. vanligtvis upp till 10 MHz i standardserielägen).Enheten kräver en kort fördröjning (cirka 200 ms) efter uppstart för den interna startåterställningen för att stabilisera.Dessutom bör alla konfigurationssignaler vara rena, brusfria och ordentligt avslutade.Om man använder varmtänkande måste man se till att man säkerställer signalintegritet och korrekt sekvensering av kraft och I/O.

EPF6016ATC144-2N Fördelar

• Kostnadseffektivt för mitten av komplexitetsdesign

EPF6016ATC144-2N har en balans mellan överkomliga priser och funktionalitet, vilket gör den idealisk för mönster som kräver mer flexibilitet än fast logik men motiverar inte kostnaden eller kraftöversikten för avancerade FPGA: er.

• Förenklad PCB -design och integration

Jämfört med FPGA: er med högre densitet som ofta kräver BGA-paket med finhopp, finns EPF6016ATC144-2N i ett standard 144-stifts TQFP-paket.Denna förpackning förenklar både design och tillverkning av PCB eftersom den undviker behovet av avancerade layoutverktyg, mikrovier eller kostsamma högskiktsavtal.Det underlättar också handlönande eller grundläggande omarbetning, vilket är fördelaktigt för mindre team eller labb med begränsade monteringskapaciteter.

• Låg risk för föråldring under utplacering

På grund av dess långvariga stöd i äldre industriella applikationer förblir EPF6016ATC144-2N fortfarande tillgängligt på många sekundära marknader och stöds fortfarande allmänt i designprogramvara som Quartus II och Max+Plus II.För företag som upprätthåller långa lifecycle-produkter som fabriksautomation, mätsystem eller telekommoduler, säkerställer detta fortsatt tillgång till känt-bra kisel utan att behöva omformulera hårdvara kring nyare, mer komplexa FPGA: er.

• Pålitligt beteende

Till skillnad från några nyare högpresterande FPGA: er som arbetar vid trånga marginaler och är känsliga för kraft- och temperaturfluktuationer, är EPF6016ATC144-2N robust och tolerant för vanliga miljövariationer.Den fungerar bekvämt inom det kommersiella temperaturområdet och stöder hot-hocking, vilket gör det tillförlitligt i modulära eller användbara system.Denna tillförlitlighet gör det till ett praktiskt val för system som kräver konsekvent prestanda över tid och under variabla förhållanden.

• Långsiktig designstabilitet

I scenarier där långsiktig tillgänglighet och designfrysning är viktigare än banbrytande prestanda är den här enheten en solid kandidat.När logiken har validerats och konfigurationsfilen är inlåst kan hela systemet förbli oförändrat i flera år, till och med decennier.Detta är en stor fördel inom flyg-, transport- och militära tillämpningar där reklamifiering av nya delar är dyr eller opraktisk.

EPF6016ATC144-2N förpackningsdimensioner

Pakettyp: TQFP-144 (Thin Quad Flat Package)

Kroppsstorlek: 20 mm × 20 mm

Stifthöjd: 0,5 mm

Räkning: 144 stift

Pakethöjd: 1,0 mm

Blyramtyp: Gull-Wing leder på alla fyra sidor

Monteringstyp: Surface-Mount (SMT)

EPF6016ATC144-2N Tillverkare

EPF6016ATC144-2N tillverkades ursprungligen av Anläggningsföretag, en pionjär inom utvecklingen av fältprogrammerbara grindarrayer (FPGA).2015 förvärvades altera av Intel Corporationoch enheten är nu officiellt listad under Intels programmerbara lösningsgrupp, som hanterar och stöder Alteras Legacy FPGA -produktlinjer.Även om EPF6016ATC144-2N är en del av en avvecklad familj, förblir Intel den formella tillverkaren och vårdnadshavaren för denna enhet, underhåll av dokumentation, arkiverat stöd och livscykelmeddelanden under Intel-varumärket.

Slutsats

EPF6016ATC144-2N är en flexibel och pålitlig FPGA för många olika projekt.Det erbjuder en bra mängd logikkraft, många inmatnings-/utgångsstift och enkla uppdateringar i systemet.Dess design stöder blandade spänningssystem, snabb datarörelse och omprogrammering utan att ta bort den från ett bräde.Det används ofta i saker som kontrollsystem, signalbehandling, kommunikationslänkar och testutrustning.Med starkt stöd, lång tillgänglighet och enkel förpackning är det fortfarande ett smart val som behöver en kostnadseffektiv och stabil lösning.

Datablad pdf

EPF6016ATC144-2N Datablad:

Om oss

ALLELCO LIMITED

Läs mer

Snabb förfrågan

Skicka en förfrågan, vi svarar omedelbart.

Vanliga frågor [FAQ]

1. Vilka verktyg behöver jag för att programmera EPF6016ATC144-2N idag?

Du kan använda Intels Legacy Quartus II eller Max+Plus II -programvara för utveckling och sammanställning.För programmering förblir verktyg som USB-Blaster-kabeln och Quartus-programmeraren kompatibla för konfiguration.

2. Är EPF6016ATC144-2N lämplig för små produktionskörningar eller prototyper?

Ja.Dess TQFP-144-paket gör det enkelt att prototyp utan behov av avancerade monteringverktyg.Det är också idealiskt för småskalig produktion där låg kostnad och flexibilitet behövs.

3. Hur jämför EPF6016ATC144-2N med nyare FPGA när det gäller prestanda?

Även om det inte är lika funktionsrikt som moderna avancerade FPGA: er, erbjuder EPF6016ATC144-2N pålitlig prestanda för måttlig logikkomplexitet med lägre kraftförbrukning och enklare integration, vilket gör det kostnadseffektivt för många applikationer.

4. Är det säkert att hett plugg EPF6016ATC144-2N i livesystem?

Ja.Denna FPGA stöder hot-socking för 3.3V-system, vilket gör att den kan infogas eller tas bort utan att stänga av värdkortet, perfekt för fälttjänst eller modulära hårdvarukonstruktioner.

5. Varför ska jag välja EPF6016ATC144-2N över anpassade ASIC- eller CPLD-lösningar?

EPF6016ATC144-2N erbjuder snabbare utvecklingscykler, omprogrammering i fältet och minskade kostnader i förväg jämfört med ASIC.Jämfört med CPLD ger det mer logikkapacitet och flexibel routing, idealisk för skalbara och utvecklande mönster.

LC5768MC-75F256C CPLD: Funktioner, specifikationer, fördelar och applikationer

på 2025/07/10

Komma igång med MC7447AHX1000NB

på 2025/07/10

Populära inlägg

-

Komplexa instruktionsuppsättningsdatorer: Hur de ändrade datoranvändning?

på 8000/04/19 147780

-

USB-C-pinout och funktioner

på 2000/04/19 112050

-

Använda Xilinx Unified Simulation Primitives: En omfattande guide till FPGA -design och simulering

på 1600/04/19 111352

-

Strömförsörjningsspänningar i elektronik: Betydelsen av VCC, VDD, VEE, VSS och GND

på 0400/04/19 83806

-

RJ45 -anslutningsguide: Pinout, ledningar, kabeltyper och användningar

på 1970/01/1 79608

-

Den ultimata guiden för trådfärgkoder i moderna elektriska system

Hur våra elektriska system använder färger är inte bara för utseende.Varje trådfärg indikerar nu en specifik funktion, vilket gör det lättare att identifiera och hantera elektriska komponenter korr...på 1970/01/1 66991

-

Purge Valve Guide: Funktion, symtom, testning och ersättning för optimal motorprestanda

Purge -ventilen är en viktig del av bilens system som hjälper till att hålla luften ren genom att hantera bränsleångor innan de kan fly in i atmosfären.Detta hjälper inte bara miljön genom att mins...på 1970/01/1 63113

-

Kvalitet (Q) Faktor: Ekvationer och applikationer

Kvalitetsfaktorn, eller 'Q', är viktig när man kontrollerar hur väl induktorer och resonatorer arbetar i elektroniska system som använder radiofrekvenser (RF).'Q' mäter hur väl en krets minimerar e...på 1970/01/1 63050

-

Uppnå toppprestanda med den maximala kraftöverföringssatsen

Den maximala kraftöverföringssatsen förklarar hur energi från en källa, till exempel ett batteri eller generator, flyter till en ansluten belastning.Det visar det exakta tillståndet där lasten får ...på 1970/01/1 54097

-

A23 -batterispecifikationer och kompatibilitet

A23-batteriet är ett litet, cylinderformat batteri med högspänning.Även kallad 23A, 23AE eller MN21, den körs vid 12 volt och mycket högre än AA- eller AAA -batterier.Dess speciella design...på 1970/01/1 52199