EPM7256SQC208-10 Guide: Funktioner, pinout, programmering, applikationer och datablad

Den här guiden handlar om EPM7256SQC208-10, en typ av programmerbart chip tillverkat av Intel (ursprungligen av Altera).Det kommer från Max® 7000S -familjen och är känd för att vara snabb, pålitlig och lätt att programmera medan den redan finns i en enhet.Den här artikeln förklarar vad chipet gör, hur det fungerar, var det används och varför det är ett bra val om du behöver en stark och flexibel logikenhet för ditt projekt.Katalog

EPM7256SQC208-10 Översikt

De EPM7256SQC208-10 är en del av Intels (tidigare Altera) Max® 7000S-familj, ett högpresterande CPLD-sortiment känt för sina robusta programmerbarhet och logiska optimeringsfunktioner.Denna modell har cirka 5 000 användbara grindar och inkluderar 256 makroceller, inrymda i en 208-stifts plastfyrat plattpack (PQFP).Den arbetar med en frekvens upp till 128,2 MHz och stöder en 5,0 V driftspänning, med en maximal förökningsfördröjning på 7,5 ns och ett driftstemperaturtak på +70 ° C.En nyckelfunktion är dess programmerbarhet i systemet genom en inbyggd IEEE STD.1149.1 JTAG -gränssnitt, möjliggör dynamisk konfiguration.Max® 7000S-enheterna tillverkas med avancerad CMOS-teknik, och erbjuder funktioner som PIN-TO-PIN LOGIC-förseningar så snabba som 5 NS och motfrekvenser som når upp till 175,4 MHz.Familjen presenterar en mängd olika paketalternativ och är utformad med programmerbara makrocellflip-flops som bidrar till betydande kraftbesparingar över 50% minskning i vissa fall.Dessutom inkluderar den en säkerhetsbit för skyddet av äganderätt.

Om din organisation behöver en solid programmerbar logiklösning är EPM7256SQC208-10 ett pålitligt val, så kontakta oss idag för att säkra din bulkorder.

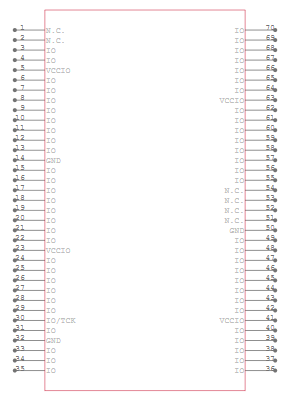

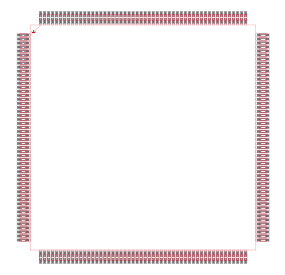

EPM7256SQC208-10 CAD-modeller

EPM7256SQC208-10 Symbol

EPM7256SQC208-10 fotavtryck

EPM7256SQC208-10 3D-modell

EPM7256SQC208-10 Funktioner

• Hög logisk täthet: EPM7256SQC208-10 ger cirka 5 000 användbara grindar och innehåller 256 makroceller.Denna höga logikkapacitet gör den idealisk för att implementera komplexa kombinationskretsar och effektiv logikintegration i kompakta mönster.

• Snabbprestanda: Med en maximal driftsfrekvens på 128,2 MHz och en förökningsfördröjning på bara 7,5 ns säkerställer denna CPLD snabba bearbetning och snabba responstider, bra för höghastighetsapplikationer.

• Programmerbarhet i systemet (ISP): Utrustad med en IEEE STD.1149.1 JTAG-gränssnitt, enheten möjliggör programmering och testning i systemet utan behov av fysiskt borttagning, underlättar iterativ utveckling och uppdateringar.

• Avancerad arkitektur: Med hjälp av Alteras andra generationens max-arkitektur och tillverkad med avancerad CMOS-teknik erbjuder EPM7256SQC208-10 förbättrad prestanda och hållbarhet, vilket säkerställer tillförlitlighet i olika operativa miljöer.

• Krafthantering: Enheten har programmerbara strömbesparande lägen som kan minska strömförbrukningen med över 50% per makrocell, stödja energieffektiva mönster och förlänga batteritiden i bärbara applikationer.

• Säkerhetsfunktioner: En programmerbar säkerhetsbit ger skydd mot obehörig åtkomst och kopiering av egenutvecklade mönster och skyddar immateriell egendom effektivt.

• Breda driftsförhållanden: Arbetar vid 5,0 V och kan fungera i temperaturer upp till +70 ° C, denna CPLD anpassar sig till olika miljöförhållanden, vilket gör den lämplig för både industriella och kommersiella applikationer.

• Flexibla I/O -standarder : Stöder Multivolt ™ I/O -gränssnittsoperationer, kompatibla med både 3,3 V- och 5,0 V -system.Denna flexibilitet möjliggör sömlös integration med befintlig och ny hårdvara, vilket minskar systemkomplexiteten och kostnaderna.

• Konstruktionsstöd: EPM7256SQC208-10 stöds av en rad designverktyg och programmeringsmaskinvarualternativ, förenkla utvecklingsprocessen och låta fokus på innovation snarare än kompatibilitetsproblem.

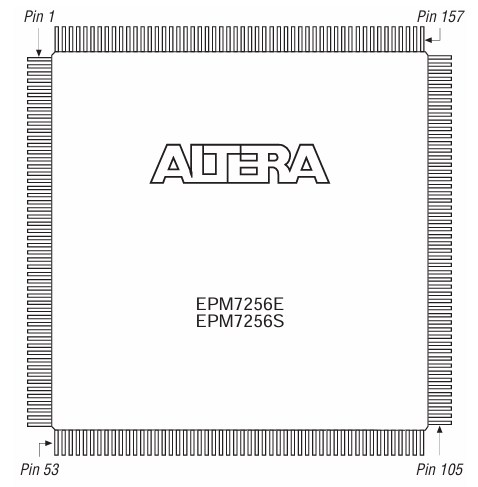

EPM7256SQC208-10 PINOUT DIAGRAM

Detta diagram visar PIN-layouten för EPM7256SQC208-10-chipet från Altera.Chipet har 208 stift, arrangerat på alla fyra sidor i en fyrkantig form.Stift 1 börjar vid det övre vänstra hörnet och siffrorna går runt chipet i en moturs riktning, ner på vänster sida till stift 53, över botten till stift 105, upp till höger till stift 157 och tillbaka till den övre höger.Etiketterna hjälper dig att veta var du ska börja och hur du placerar chipet korrekt på ett kretskort.Namnet i mitten, "EPM7256E / EPM7256S," betyder att denna layout fungerar för båda chipversionerna.Detta diagram är viktigt när du ansluter kraft, signaler eller programmeringslinjer till chipet.

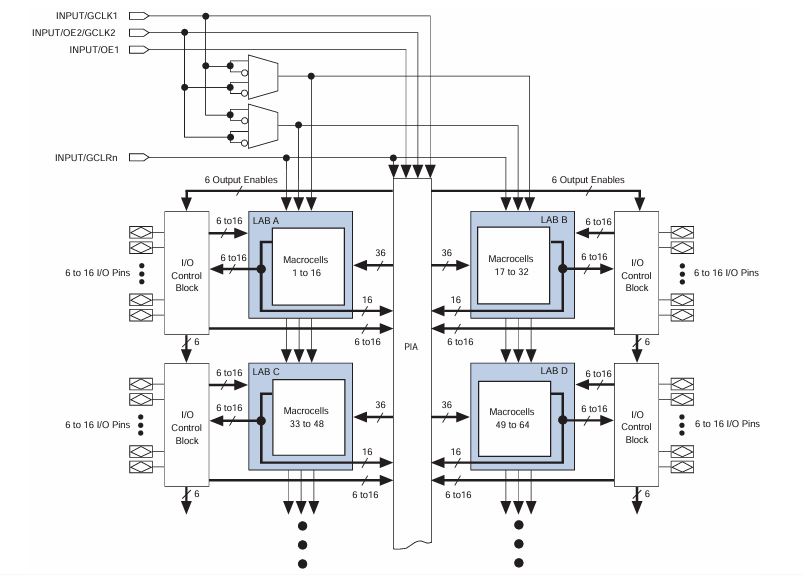

EPM7256SQC208-10 BLOCK DIAGRAM

Blockdiagrammet för EPM7256SQC208-10 visar hur chipet är organiserat för att hantera digitala logikuppgifter.Den har fyra huvudsakliga logikblock som kallas lab A, B, C och D. Varje block innehåller 16 makroceller, som är de grundläggande byggnadsdelarna som gör logikarbetet.Så totalt finns det 64 makroceller inuti chipet.Runt dessa logikblock finns I/O -kontrollblock, som förbinder chipet till omvärlden genom input och utgångsstift.Varje kontrollblock hanterar 6 till 16 stift och låter signaler gå in eller ut ur chipet efter behov.

I mitten är den programmerbara interconnect -arrayen (PIA), som fungerar som ett motorvägssystem, som låter signaler flytta mellan logikblock och I/O -stift.Detta gör att du kan dirigera data på vilket sätt du behöver för din design.Längst upp till vänster visar diagrammet några kontrollingångar som Global Clock (GCLK), utgångsaktivering (OE) och CLEAR (GCLR).Dessa signaler hjälper till att hantera tidpunkten och beteendet hos logikkretsarna över chipet.

EPM7256SQC208-10 Specifikationer

|

Typ |

Parameter |

|

Tillverkare |

Altera/intel |

|

Serie |

Max® 7000s |

|

Förpackning |

Bricka |

|

Delstatus |

Föråldrad |

|

Programmerbar typ |

I systemprogrammerbar |

|

Fördröjningstid TPD (1) Max |

10 ns |

|

Spänningsförsörjning - intern |

4.75V ~ 5.25V |

|

Antal logikelement/block |

16 |

|

Antal makroceller |

256 |

|

Antal grindar |

5000 |

|

Antal I/O |

164 |

|

Driftstemperatur |

0 ° C ~ 70 ° C (TA) |

|

Monteringstyp |

Ytfäste |

|

Förpackning / fodral |

208-bfqfp |

|

Leverantörspaket |

208-PQFP (28x28) |

|

Basproduktnummer |

EPM7256 |

EPM7256SQC208-10 Applikationer

Industriautomation

EPM7256SQC208-10 används i stor utsträckning i industriella automatiseringssystem.Dess höga logikdensitet och snabba prestanda möjliggör komplexa kontrolluppgifter och gränssnitt sömlöst med sensorer och ställdon.Denna CPLD är idealisk för att förbättra precisionen och effektiviteten i produktionslinjer, processkontrollsystem och robotapplikationer.

Telekommunikation

På telekommunikation utmärker denna CPLD att hantera dataflöde och signalintegritet över nätverk.Det stöder funktioner som signalomvandling, routing och bearbetning i switchar och routrar, vilket säkerställer robusta och effektiva kommunikationsinfrastrukturer.

Bilsystem

Inom fordonsindustrin bidrar denna enhet till tillförlitligheten och sofistikeringen av system som motorhanteringsenheter, infotainmentsystem och förar-assistance-teknik.Dess robusta prestanda under varierande förhållanden gör den lämplig för säkerhetskritiska applikationer.

Medicinsk utrustning

Precisionen och programmerbarheten för EPM7256SQC208-10 gör det värdefullt inom medicinsk utrustning, där korrekt kontroll och tillförlitlig drift är viktiga.Det används i enheter för att övervaka patientens vitaler, hantera diagnostiska instrument och automatisera behandlingsleverans.

Flyg- och försvar

I flyg- och försvaret används EPM7256SQC208-10 i system som kräver höga nivåer av tillförlitlighet och prestanda, såsom satellitkommunikation, navigationshjälpmedel och militära hårdvarukontroller.Dess förmåga att arbeta under extrema förhållanden är fördelaktigt.

Utbildnings- och forskningsinstitutioner

Denna CPLD är också populär i utbildningsmiljöer och forskningsprojekt, där dess omprogrammerbarhet och flexibilitet underlättar experiment och lärande inom digital design och elektronik.Det gör det möjligt att prototypa och testa olika logikkonstruktioner effektivt.

EPM7256SQC208-10 Liknande delar

EPM7256SQC208-10 Programmeringssteg

1. Ange ISP -läge

Detta första steg är viktigt när det övergår CPLD från normalt driftsläge till in-system-programmeringsläge (ISP).Detta uppnås genom att skicka ett specifikt kommando via JTAG -gränssnittet.Under denna process är alla I/O-stift av CPLD tri-statliga (inaktiverade) för att undvika störningar eller konflikter med andra kretskomponenter.Övergången till ISP -läge förbereder enheten för säker programmering och tar cirka 1 millisekund.

2. Kontrollera ID

När en gång är i ISP -läge utför systemet en ID -kontroll för att säkerställa att rätt enhet programmeras.Detta innebär att läsa enhetens unika kisel -ID genom JTAG -gränssnittet.Detta steg är bra för att verifiera att programmeringskommandon och data kommer att skickas till rätt enhet, vilket förhindrar felaktig programmering och potentiell enhetsskada.

3. Bulkrad

Innan nya data kan programmeras måste de befintliga uppgifterna inom CPLD raderas.Steget med bulkrader rensar effektivt alla programmerbara celler i enheten.Detta görs genom att växla i raderingsinstruktionen och sedan tillämpa en 100-millisekund puls som raderar hela chipet.Detta steg är viktigt för att säkerställa att inga rester av tidigare konfigurationer stör den nya programmeringen.

4. program

Detta steg involverar den faktiska programmeringen av CPLD där de nya konfigurationsdata skrivs in i enheten.Data och motsvarande adresser flyttas till enheten via JTAG -gränssnittet.Varje adress och datapar kräver en programmeringspuls för att säkerställa att data är korrekt skrivna i de icke-flyktiga minnescellerna i CPLD.Detta steg upprepas för varje datapunkt över enhetens minneskarta.

5. Verifiera

Efter programmering är det behov av att verifiera att uppgifterna har skrivits korrekt till enheten.Detta verifieringssteg innebär att läsa tillbaka de programmerade uppgifterna från varje adress och jämföra dem med de ursprungliga inmatningsdata.Detta steg säkerställer dataintegritet och bekräftar att programmeringsprocessen har varit framgångsrik utan några fel.

6. EXIT ISP -läge

Det sista steget i programmeringsprocessen är att lämna ISP -läget och returnera CPLD till normalt driftsläge.Detta görs genom att skicka ett annat kommando via JTAG -gränssnittet.Vid framgångsrik utgång återaktiveras I/O -stiften och enheten återupptas normal funktion.Detta steg tar också vanligtvis cirka 1 millisekund.

EPM7256SQC208-10 Fördelar

Icke-flyktig konfiguration

EPM7256SQC208-10 använder EEPROM-teknik, vilket gör att den kan lagra sin konfiguration permanent.Denna icke-flyktiga natur innebär att enheten inte behöver ladda om sina konfigurationsdata från externt minne varje gång den är påslagen.Detta resulterar i snabbare starttider och minskar den övergripande komplexiteten i hårdvarukonstruktionen genom att eliminera behovet av ytterligare konfigurationslagringskomponenter.

Programmerbarhet i systemet (ISP)

En av de framstående funktionerna i EPM7256SQC208-10 är dess stöd för programmerbarhet i systemet.Detta gör att enheten kan programmeras och omprogrammeras medan den är inbäddad i slutapplikationen utan att behöva tas bort fysiskt.Denna kapacitet förenklar uppdateringar och modifieringar, vilket ger flexibilitet och användarvänlighet under utvecklingen och under hela produktens livscykel.

Hög I/O -räkning och logisk densitet

Enheten erbjuder en betydande mängd logikresurser och I/O -stift, med 256 makroceller och 164 användar I/O -stift.Denna höga I/O -räkning och logikdensitet möjliggör integration av flera funktioner i ett enda chip, vilket underlättar mer komplexa mönster samtidigt som man bevarar utrymme på PCB.Denna fördel är fördelaktig i applikationer där styrelseutrymmet är på en premium och multifunktionalitet är viktig.

Snabb stift-till-pin-fördröjning

Med en maximal stift-till-pin-fördröjning på bara 10 ns kan EPM7256SQC208-10 utföra höghastighetslogikoperationer.Denna snabba responstid är bra i applikationer som kräver snabba behandlingsfunktioner, såsom höghastighetskommunikation eller datoranvändning, vilket säkerställer att systemet uppfyller stränga prestandakriterier.

Bredspänningskompatibilitet

EPM7256SQC208-10 är utformad för att vara flexibel när det gäller spänningskompatibilitet, vilket stödjer intern drift vid 5 V- och I/O-nivåer vid 3,3 V. Denna dubbelspänningskapacitet gör det möjligt att gränssnittet kan enkelt gränssnittet med både 3,3 V och 5 V-system, vilket minskar behovet av översättningsnivåöversättare och förenklande systemdesign.

EPM7256SQC208-10 Förpackningsdimensioner

• Pakettyp: 208-bfqfp (plast quad platt paket)

• Antal stift: 208 leder

• Kroppsstorlek (L × W): 28 mm × 28 mm

• Monteringsstil: Surface Mount Technology (SMT)

• Blyplan: Vanligtvis 0,5 mm mellan stift (standard för BFQFP)

• Förpackningsmaterial: Plastisk

• Pakettjocklek: Cirka 3,5 mm (varierar något av tillverkaren)

• Termiska egenskaper: Ingen exponerad dyna;Standard Ambient Dissipation via brädet

• Brickförpackning: Levereras i brickor för volymhantering och plockningsautomation

EPM7256SQC208-10 Tillverkare

EPM7256SQC208-10 utvecklades och tillverkades ursprungligen av Anläggningsföretag, en ledande pionjär inom programmerbara logikenheter som är kända för sin Max® 7000S -serie med CPLD.2015 förvärvades altera av Intel Corporation, en av världens största halvledartillverkare.Sedan förvärvet har Intel fortsatt att stödja och integrera Alteras CPLD- och FPGA -teknik under sin programmerbara lösningsgrupp.EPM7256SQC208-10 representerar Intels arv i att erbjuda högpresterande, programmerbara logiklösningar i systemet skräddarsydda för ett brett spektrum av industriella, telekommunikation och inbäddade applikationer.Även om det nu klassificeras som föråldrat, återspeglar delen Intels långvariga engagemang för pålitliga och flexibla programmerbara logikenheter.

Slutsats

EPM7256SQC208-10 är ett smart och pålitligt chip som hjälper dig att få digitala system att fungera smidigt.Det sparar ström, stöder olika spänningar och låter dig programmera den medan den redan är installerad, vilket gör uppdateringar enkelt.Även om det nu är ett äldre chip, använder andra fortfarande det eftersom det fungerar bra i alla typer av system.Om du behöver ett solid chip för att kontrollera logik i din design är det här ett bra alternativ.Kontakta oss idag om du vill beställa den i bulk.

Datablad pdf

EPM7256SQC208-10 Datablad:

Programvaruskiva 06/nov/2020.pdf

Cylindriska batterilhållare.pdf

Om oss

ALLELCO LIMITED

Läs mer

Snabb förfrågan

Skicka en förfrågan, vi svarar omedelbart.

Vanliga frågor [FAQ]

1. Vilka programmeringsverktyg är kompatibla med EPM7256SQC208-10?

Du kan använda Intels programvara Quartus II (tidigare Altera Quartus), tillsammans med en JTAG-kompatibel programmerare som USB-Blaster, för att konfigurera och programmera EPM7256SQC208-10 direkt i systemet.

2. Kan jag omprogrammera EPM7256SQC208-10 flera gånger?

Ja, EPM7256SQC208-10 stöder flera omprogrammeringscykler med hjälp av sina EEPROM-baserade programmerbarhet i systemet, vilket gör det idealiskt för iterativ designutveckling eller uppdateringar efter utplacering.

3. Kan EPM7256SQC208-10 hantera hårda driftsförhållanden?

Det fungerar pålitligt inom ett kommersiellt temperaturintervall av 0 ° C till +70 ° C, vilket är tillräckligt för de flesta industriella och inbäddade applikationer, men inte för extrema miljöer eller bilkvalitet.

4. Kan jag fortfarande programmera EPM7256SQC208-10 utan att ta bort det från kretskortet?

Ja.Chip stöder programmerbarhet i systemet (ISP) via JTAG, så att du kan omprogrammera den medan den redan lödas på ditt bräde, vilket sparar tid och ansträngning under utveckling eller underhåll.

5. Vad gör EPM7256SQC208-10 bättre än en standardmikrokontroller för logiska uppgifter?

Till skillnad från mikrokontroller är EPM7256SQC208-10 en CPLD, som utmärker sig vid att utföra parallella logiska operationer med exakt tidpunkt.Det är perfekt när du behöver snabb, deterministisk digital kontroll över flera signaler.

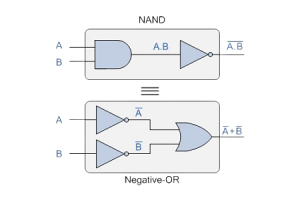

Demorgan's Theorem förklarade: förenklande logikuttryck för bättre kretsdesign

på 2025/04/25

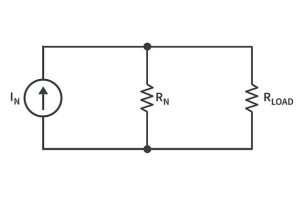

Norton teorem grunder och kretsexempel

på 2025/04/24

Populära inlägg

-

Komplexa instruktionsuppsättningsdatorer: Hur de ändrade datoranvändning?

på 8000/04/18 147765

-

USB-C-pinout och funktioner

på 2000/04/18 111994

-

Använda Xilinx Unified Simulation Primitives: En omfattande guide till FPGA -design och simulering

på 1600/04/18 111351

-

Strömförsörjningsspänningar i elektronik: Betydelsen av VCC, VDD, VEE, VSS och GND

på 0400/04/18 83751

-

RJ45 -anslutningsguide: Pinout, ledningar, kabeltyper och användningar

på 1970/01/1 79548

-

Den ultimata guiden för trådfärgkoder i moderna elektriska system

Hur våra elektriska system använder färger är inte bara för utseende.Varje trådfärg indikerar nu en specifik funktion, vilket gör det lättare att identifiera och hantera elektriska komponenter korr...på 1970/01/1 66949

-

Purge Valve Guide: Funktion, symtom, testning och ersättning för optimal motorprestanda

Purge -ventilen är en viktig del av bilens system som hjälper till att hålla luften ren genom att hantera bränsleångor innan de kan fly in i atmosfären.Detta hjälper inte bara miljön genom att mins...på 1970/01/1 63094

-

Kvalitet (Q) Faktor: Ekvationer och applikationer

Kvalitetsfaktorn, eller 'Q', är viktig när man kontrollerar hur väl induktorer och resonatorer arbetar i elektroniska system som använder radiofrekvenser (RF).'Q' mäter hur väl en krets minimerar e...på 1970/01/1 63028

-

Uppnå toppprestanda med den maximala kraftöverföringssatsen

Den maximala kraftöverföringssatsen förklarar hur energi från en källa, till exempel ett batteri eller generator, flyter till en ansluten belastning.Det visar det exakta tillståndet där lasten får ...på 1970/01/1 54094

-

A23 -batterispecifikationer och kompatibilitet

A23-batteriet är ett litet, cylinderformat batteri med högspänning.Även kallad 23A, 23AE eller MN21, den körs vid 12 volt och mycket högre än AA- eller AAA -batterier.Dess speciella design...på 1970/01/1 52175