Förbättra FPGA -design med användarbegränsningsfiler (UCF) för Xilinx ISE -verktyg

Den här guiden undersöker rollen för användarbegränsningsfiler (UCFS) för att förbättra FPGA -design med Xilinx ISE -verktyg.UCF: er tillåter att lägga till specifika begränsningar för att bättre kontrollera timing, logik och placering, vilket ökar designnoggrannheten, prestanda och tillförlitlighet.Genom att visa hur man använder dessa begränsningar effektivt hjälper guiden att förenkla designprocessen, minska felsökningstiden och säkerställa framgångsrik projektleverans.Katalog

UCF: s syfte och roll i FPGA -design

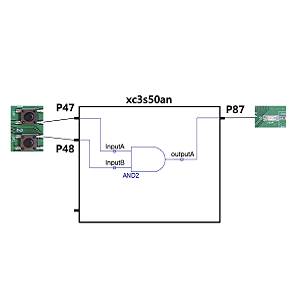

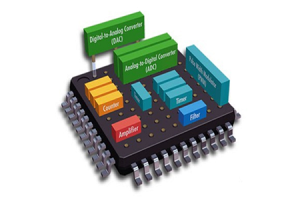

I FPGA -design spelar användarbegränsningsfiler (UCFS) en roll för att kontrollera hur den logik som syntetiseras från din kod fysiskt implementeras på chipet.Dessa filer låter specificera viktiga parametrar som tidsbegränsningar, stifttilldelningar och information om områdesplacering som direkt kan påverka om en design uppfyller prestandakraven eller inte.Tänk på UCF: er som ritningar som säkerställer att allt är placerat korrekt, fungerar enligt schema och passar snyggt på plats.Processen för begränsningsinställning börjar i de tidiga utvecklingsstadierna.Börja med att skapa en UCF -fil före syntes och se till att parametrar är inlåsta redan från början.Efter syntes genereras ytterligare begränsningsfiler som NetList Constraint -filen (NCF) och fysisk begränsningsfil (PCF) för att återspegla förändringar som gjorts i logiken och för att slutföra fysiska begränsningar.Var och en av dessa filer bygger på föregående steg och förädlar gradvis designen.UCF: er är textbaserade filer skrivna i ASCII-format, vilket innebär att de kan redigeras med grundläggande textredaktörer eller mer specialiserade verktyg som Xilinx-begränsningsredigeraren.Denna enkelhet gör UCF: er mycket tillgängliga och flexibel att dyka in i specifikationerna för begränsningsinställningar utan att behöva alltför komplexa verktyg.

Hur begränsningar formar FPGA -design?

I FPGA -design spelar begränsningar en roll i att forma hur chipet presterar och interagerar med externa enheter.Dessa begränsningar definieras i en UCF (användarbegränsningsfil), som fungerar som en detaljerad instruktionsuppsättning för designverktyget, vilket specificerar hur FPGA: s interna komponenter ska anslutas och hanteras.Viktiga begränsningar inkluderar tidsbegränsningar, som säkerställer signaler mellan komponenter inom en viss tidsram för att upprätthålla tillförlitlig prestanda med önskad klockhastighet.PIN -tilldelningar kartlägger fysiska FPGA -stift till externa enheter som sensorer, minnesmoduler eller kommunikationsgränssnitt, vilket säkerställer exakta anslutningar.Områdesbegränsningar styr placeringen av logikblock på chipet för att undvika trängsel, minska förseningar och optimera resursanvändningen.Utan dessa begränsningar skulle automatiserade verktyg fatta beslut om placering och routing, men ofta med suboptimala resultat, vilket leder till tidsproblem, flaskhalsar eller ineffektiva chiplayouter.Genom att använda UCF -filer behåller många kontroll över dessa kritiska aspekter, vilket resulterar i bättre prestanda, effektivitet och tillförlitlighet i FPGA -mönster.

Den iterativa karaktären av begränsningsförfining

FPGA-design är sällan en en-och-gjort-process.Begränsningar justeras upprepade gånger under utvecklingscykeln när designen utvecklas och nya utmaningar dyker upp.Andra justerar UCF -filer för att uppfylla prestandamål, fixa timingproblem eller anpassa sig till förändrade projektkrav.Denna iterativa förfining är en viktig del av FPGA -arbetsflödet.Om du till exempel märker att en signalväg tar för lång tid för att sprida mellan två komponenter, kan de ändra UCF för att ändra tidsbegränsningen eller flytta dessa komponenter för att minska förseningar.På samma sätt, om en PIN -tilldelning konflikter med extern hårdvara, kan UCF redigeras för att lösa missanpassningen.Varje revision av UCF flyttar designen närmare det önskade resultatet, med varje justering som undervisar mer om de avvägningar som är involverade i FPGA-optimering.Denna cykel av testning, justering och lärande förbättrar inte bara designen utan skärper också färdigheter.

Fördelar med att använda UCF: er

Att tillämpa begränsningar genom UCF -filer ger flera praktiska fördelar som bidrar till framgången för FPGA -projekt:

• Förbättrad tidsnoggrannhet: Välformade tidsbegränsningar säkerställer att FPGA fungerar pålitligt med önskad klockhastighet och undviker fel orsakade av signalförseningar.

• Bättre resursanvändning: Begränsningar av området förhindrar att logiska block placeras för nära varandra eller för långt ifrån varandra, optimerar chiputrymmet och förbättrar prestandan.

• Förenklad felsökning: Genom att kontrollera PIN -tilldelningar och signalruttning hjälper UCF: er att minska routingkonflikter, vilket gör det enklare att diagnostisera och fixa problem under testning.

Om oss

ALLELCO LIMITED

Läs mer

Snabb förfrågan

Skicka en förfrågan, vi svarar omedelbart.

Applikationsspecifika standardprodukter (ASSP): Körande innovation inom modern elektronik

på 2025/01/8

System på ett programmerbart chip (SOPC): teknik, design och applikationer

på 2025/01/8

Populära inlägg

-

Komplexa instruktionsuppsättningsdatorer: Hur de ändrade datoranvändning?

på 8000/04/18 147776

-

USB-C-pinout och funktioner

på 2000/04/18 112018

-

Använda Xilinx Unified Simulation Primitives: En omfattande guide till FPGA -design och simulering

på 1600/04/18 111351

-

Strömförsörjningsspänningar i elektronik: Betydelsen av VCC, VDD, VEE, VSS och GND

på 0400/04/18 83775

-

RJ45 -anslutningsguide: Pinout, ledningar, kabeltyper och användningar

på 1970/01/1 79571

-

Den ultimata guiden för trådfärgkoder i moderna elektriska system

Hur våra elektriska system använder färger är inte bara för utseende.Varje trådfärg indikerar nu en specifik funktion, vilket gör det lättare att identifiera och hantera elektriska komponenter korr...på 1970/01/1 66962

-

Purge Valve Guide: Funktion, symtom, testning och ersättning för optimal motorprestanda

Purge -ventilen är en viktig del av bilens system som hjälper till att hålla luften ren genom att hantera bränsleångor innan de kan fly in i atmosfären.Detta hjälper inte bara miljön genom att mins...på 1970/01/1 63103

-

Kvalitet (Q) Faktor: Ekvationer och applikationer

Kvalitetsfaktorn, eller 'Q', är viktig när man kontrollerar hur väl induktorer och resonatorer arbetar i elektroniska system som använder radiofrekvenser (RF).'Q' mäter hur väl en krets minimerar e...på 1970/01/1 63041

-

Uppnå toppprestanda med den maximala kraftöverföringssatsen

Den maximala kraftöverföringssatsen förklarar hur energi från en källa, till exempel ett batteri eller generator, flyter till en ansluten belastning.Det visar det exakta tillståndet där lasten får ...på 1970/01/1 54097

-

A23 -batterispecifikationer och kompatibilitet

A23-batteriet är ett litet, cylinderformat batteri med högspänning.Även kallad 23A, 23AE eller MN21, den körs vid 12 volt och mycket högre än AA- eller AAA -batterier.Dess speciella design...på 1970/01/1 52186