Latch vs Flip-Flop: Comparison Guide for Digital Electronics

Spärrar och flip-flops är grundläggande digitala lagringselement som hjälper dig att lagra och kontrollera binära data i kretsar.I den här artikeln kommer du att lära dig vad de är, hur de fungerar och hur deras timingbeteende skiljer sig.Du kommer också att utforska deras fördelar, begränsningar och vanliga tillämpningar.Detta hjälper dig att förstå när du ska använda var och en i dina mönster.Katalog

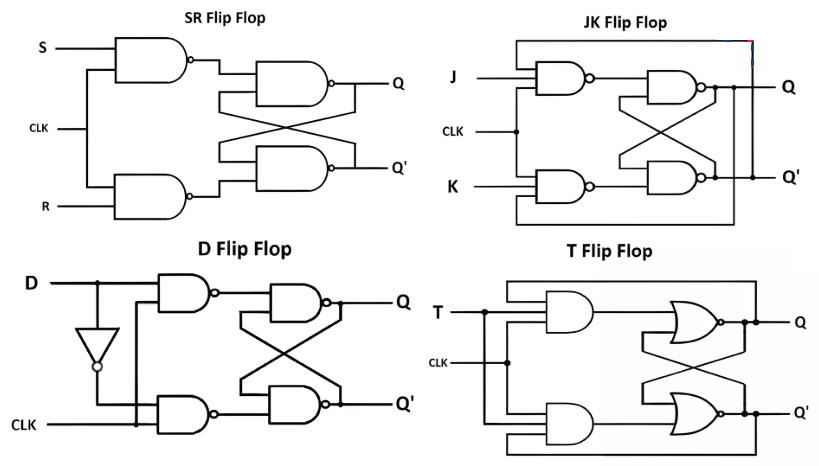

Vad är en spärr i digital elektronik?

Figur 1. Grundläggande låskretsdiagram

En spärr är ett nivåutlöst digitalt lagringselement som används för att lagra en bit binär data.Den svarar på en aktiverings- eller kontrollsignal som bestämmer när data kan lagras eller lagras.Detta gör den till en viktig komponent i grundläggande digital elektronik.Spärrar implementeras vanligtvis med enkla logiska grindkonfigurationer.De används ofta i kretsar som kräver tillfällig datalagring.

En spärr fungerar som en grundläggande minnesenhet som kan upprätthålla ett stabilt utgångsvärde.Dess struktur tillåter den att hålla ett logiskt tillstånd tills ett kontrollvillkor tillåter en uppdatering.Detta gör den lämplig för enkla lagrings- och kontrolluppgifter i digitala system.Spärrar används ofta som byggstenar i större logiska konstruktioner.Deras enkelhet gör dem effektiva för kretsar med låg komplexitet.

Vad är en flip-flop i digital elektronik?

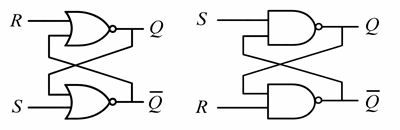

Figur 2. Grundläggande flip-flop kretsdiagram

En flip-flop är ett kantutlöst digitalt lagringselement som lagrar en bit data som svar på en klocksignal.Den är utformad för att uppdatera sitt tillstånd endast vid specifika signalövergångar.Detta kontrollerade beteende gör det viktigt i moderna digitala system.Vippor används i stor utsträckning i sekventiella logiska kretsar.De fungerar som kärnkomponenter i många elektroniska konstruktioner.

En flip-flop fungerar som en pålitlig minnesenhet som upprätthåller en stabil utsignal mellan klockhändelser.Dess design säkerställer att data lagras på ett kontrollerat och förutsägbart sätt.Olika typer av flip-flops stödjer olika logiska funktioner i digitala kretsar.Dessa enheter används ofta som byggstenar i komplexa system.Deras strukturerade beteende gör dem lämpliga för organiserad datahantering.

Latch vs flip-flop operation (timing och triggning)

Ändringar av låsläge (nivåutlöst operation)

Figur 3. Spärrnivåutlöst tidsdiagram

Spärren ändrar tillstånd kontinuerligt medan aktiveringssignalen förblir på en aktiv nivå, vilket illustreras av de markerade aktiva områdena i vågformen.Under dessa intervaller följer utgången ingången direkt, vilket möjliggör uppdateringar.Detta beteende är uppenbart i både positiv och negativ nivåtriggning, där spärren reagerar baserat på om styrsignalen är hög eller låg.När aktiveringssignalen blir inaktiv slutar utgången att uppdateras och håller det senast lagrade värdet.Vågformen visar att flera ingångsändringar kan inträffa inom en enda aktiv period, och alla reflekteras vid utgången.Denna kontinuerliga lyhördhet kallas transparens i nivåutlöst drift.Som ett resultat beror låsbeteendet på signalens varaktighet snarare än en enda övergångspunkt.

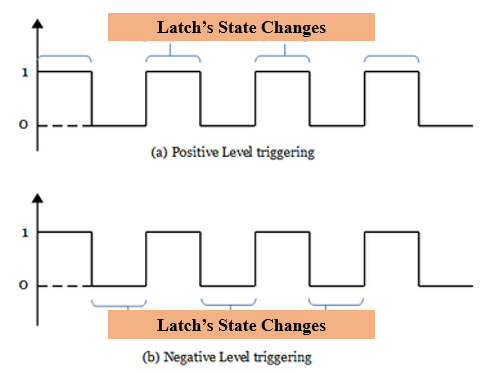

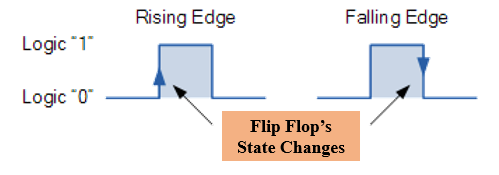

Vipplägesändringar (kantutlöst operation)

Figur 4. Flip-Flop kantutlöst tidsdiagram

Vippan ändrar tillstånd endast vid specifika övergångspunkter för klocksignalen, vilket indikeras av de stigande och fallande flankerna i vågformen.Utdata uppdateras exakt vid dessa kanter, och fångar ingångsvärdet vid det exakta ögonblicket.Mellan klockövergångarna förblir utsignalen oförändrad oavsett ingångsvariationer.Detta beteende säkerställer att dataändringar endast sker vid väldefinierade ögonblick.Diagrammet visar hur övergångskanterna fungerar som triggerpunkter för tillståndsuppdateringar.Varje kant representerar en enda möjlighet för flip-flop att lagra ny data.Denna kantutlösta mekanism ger kontrollerad och förutsägbar timing i digitala kretsar.

Fördelar och nackdelar med Latch och Flip-Flop

Fördelar med Latch och Flip-Flop

• Spärrarna ger snabbare svar tack vare kontinuerlig ingångsspårning.

• Spärrar förbrukar lägre ström i enkla konstruktioner.

• Flip-flops ger exakt timingkontroll med klocksynkronisering.

• Flipflops minskar risken för oavsiktliga tillståndsförändringar.

• Båda stöder tillförlitlig datalagring med en bit.

• Båda är viktiga för att bygga komplexa digitala system.

Begränsningar för Latch och Flip-Flop

• Spärrarna är känsliga för brus under aktiva aktiveringsperioder.

• Spärrar kan orsaka tidsosäkerhet i komplexa system.

• Flip-flops kräver fler kretsar, vilket ökar komplexiteten.

• Flipflops drar mer ström på grund av klockanvändning.

• Båda kräver noggrann timingdesign för att undvika fel.

• Båda kan introducera utbredningsfördröjning i kretsar.

Tillämpningar av spärrar och flip-flops

1. Datalagringsregister

Register använder vippor för att lagra flera databitar i processorer och digitala system.De håller tillfälligt värden under beräknings- och dataöverföringsoperationer.Detta säkerställer en stabil datahantering mellan bearbetningsstegen.Register är bra för CPU-operationer, buffring och datasynkronisering.

2. Räknare och timer

Flip-flops används ofta för att bygga digitala räknare som spårar händelser eller klockpulser.Dessa räknare är utmärkta i tidskretsar, frekvensdelning och digitala klockor.De möjliggör exakta räkneoperationer i inbyggda system.Timers litar på dem för att kontrollera förseningar och periodiska åtgärder.

3. Minneselement i digitala kretsar

Både spärrar och flip-flops fungerar som grundläggande minnesenheter inom digital elektronik.De lagrar binär data som kan nås eller ändras efter behov.Denna funktion behövs för att behålla systemtillstånd.Minneskretsar förlitar sig på dessa element för stabil drift.

4. Datasynkroniseringssystem

Flip-flops hjälper till att synkronisera signaler över olika klockdomäner i komplexa system.De säkerställer att data överförs utan tidsfel eller fel.Detta förbättrar systemets tillförlitlighet i höghastighetskonstruktioner.Synkronisering är viktigt i kommunikations- och bearbetningsenheter.

5. Styrlogikkretsar

Spärrar används i styrkretsar där omedelbar respons på ingångsändringar krävs.De hjälper till att hantera aktiveringssignaler, gating och logiskt flöde.Detta möjliggör flexibel kontroll i digitala konstruktioner.Styrlogik säkerställer korrekt systemdrift och sekvensering.

6. Skiftregister

Vippor används för att bygga skiftregister som flyttar data sekventiellt.Dessa används i dataserialisering, kommunikationssystem och signalbehandling.Skiftregister möjliggör effektiv dataöverföring mellan komponenter.De används ofta i digitala kommunikationsgränssnitt.

Skillnaden mellan flip-flop och spärr

|

Aspekt |

Spärr |

Flip-Flop |

|

Utlösare

Mekanism |

Svarar när

aktivera = HÖG eller LÅG (nivåkänslig) |

Svarar först kl

klockkant (↑ eller ↓) |

|

Styrsignal

Typ |

Aktivera (EN)

signal |

Klocka (CLK)

signal |

|

Uppdatering av data

Skick |

Uppdateringar

under hela den aktiva nivåns varaktighet |

Uppdateringar en gång per

klockkant |

|

Ingångssampling

Fönster |

Öppna fönstret

(varaktighetsbaserad) |

Omedelbar provtagning

(kantbaserat, ~ns-intervall) |

|

Typiskt

Utbredningsfördröjning |

~1–5 ns (enkel

gate fördröjning) |

~5–20 ns

(inkluderar klockkretsar) |

|

Krets

Komplexitet |

4–6 logiska grindar

(grundläggande SR-spärr) |

10–20+ grindar

(kantutlöst design) |

|

Kraft

Konsumtion |

Nedre (nr

kontinuerlig klockväxling) |

Högre (pga

klockövergångar) |

|

Byter

Frekvensgräns |

Begränsad av input

stabilitet under aktivering |

Kan fungera

tillförlitligt i intervallet 100 MHz–GHz |

|

Glitch

Känslighet |

Högre under

aktiv aktiveringsperiod |

Lägre pga

kantisolering |

|

Tidskontroll

Noggrannhet |

Beroende av

aktivera signalens varaktighet |

Definierat av

exakta klockkanter |

|

Datastabilitet

(Hold Beteende) |

Håller efter

aktivera blir inaktiv |

Håller till nästa

klockkant |

|

Klocka

Krav |

Krävs inte |

Krävs för

operation |

|

Designstil passform |

Asynkron eller

enkel kontrolllogik |

Synkron

digitala system |

|

Skalbarhet in

System |

Mindre skalbar

för stora mönster |

Mycket skalbar

i komplexa system |

|

Typiskt

Implementering Användning |

Gating, enkelt

lagring, kontrollvägar |

Register,

räknare, rörledningar |

Slutsats

Spärrar och vippor fungerar båda som viktiga enbitslagringselement men skiljer sig huvudsakligen i hur de svarar på insignaler och tidsstyrning.Spärrarna ger snabb, kontinuerlig respons genom nivåutlöst drift, medan flip-flops erbjuder exakt och stabil datahantering genom kantutlöst beteende.Var och en har sina egna fördelar och kompromisser när det gäller kraft, komplexitet och tillförlitlighet.Att välja mellan dem beror på tidskrav, systemtyp och övergripande designmål inom digital elektronik.

Om oss

ALLELCO LIMITED

Läs mer

Snabb förfrågan

Skicka en förfrågan, vi svarar omedelbart.

Vanliga frågor [FAQ]

1. Vad är den största skillnaden mellan synkrona och asynkrona lagringselement?

Synkrona element som flip-flops förlitar sig på en klocksignal, medan asynkrona element som lås fungerar baserat på ingångsnivåer utan klocka.

2. Varför föredras flipflops i klockade digitala system?

Vippor säkerställer dataändringar endast vid definierade klockkanter, vilket gör systemets timing förutsägbar och minskar fel.

3. Kan en spärr konverteras till en flip-flop?

Ja, att kombinera två spärrar i en master-slave-konfiguration kan skapa en flip-flop med kantutlöst beteende.

4. Vilka är vanliga typer av flip-flops som används i digitala kretsar?

Vanliga typer inkluderar SR, JK, D och T flip-flops, var och en designad för specifika logik- och kontrollfunktioner.

5. Hur påverkar tidsproblem spärrbaserade konstruktioner?

Felaktig timing kan orsaka fel eller tävlingsförhållanden eftersom spärrarna tillåter flera inmatningsändringar under aktiveringsperioder.

Cycloconverter Explained: Enkel guide till arbete och användning

på 2026/04/3

Jämförelseguide för LGA vs BGA för design av elektroniska system

på 2026/04/1

Populära inlägg

-

Komplexa instruktionsuppsättningsdatorer: Hur de ändrade datoranvändning?

på 8000/04/18 147772

-

USB-C-pinout och funktioner

på 2000/04/18 112011

-

Använda Xilinx Unified Simulation Primitives: En omfattande guide till FPGA -design och simulering

på 1600/04/18 111351

-

Strömförsörjningsspänningar i elektronik: Betydelsen av VCC, VDD, VEE, VSS och GND

på 0400/04/18 83769

-

RJ45 -anslutningsguide: Pinout, ledningar, kabeltyper och användningar

på 1970/01/1 79565

-

Den ultimata guiden för trådfärgkoder i moderna elektriska system

Hur våra elektriska system använder färger är inte bara för utseende.Varje trådfärg indikerar nu en specifik funktion, vilket gör det lättare att identifiera och hantera elektriska komponenter korr...på 1970/01/1 66960

-

Purge Valve Guide: Funktion, symtom, testning och ersättning för optimal motorprestanda

Purge -ventilen är en viktig del av bilens system som hjälper till att hålla luften ren genom att hantera bränsleångor innan de kan fly in i atmosfären.Detta hjälper inte bara miljön genom att mins...på 1970/01/1 63100

-

Kvalitet (Q) Faktor: Ekvationer och applikationer

Kvalitetsfaktorn, eller 'Q', är viktig när man kontrollerar hur väl induktorer och resonatorer arbetar i elektroniska system som använder radiofrekvenser (RF).'Q' mäter hur väl en krets minimerar e...på 1970/01/1 63040

-

Uppnå toppprestanda med den maximala kraftöverföringssatsen

Den maximala kraftöverföringssatsen förklarar hur energi från en källa, till exempel ett batteri eller generator, flyter till en ansluten belastning.Det visar det exakta tillståndet där lasten får ...på 1970/01/1 54097

-

A23 -batterispecifikationer och kompatibilitet

A23-batteriet är ett litet, cylinderformat batteri med högspänning.Även kallad 23A, 23AE eller MN21, den körs vid 12 volt och mycket högre än AA- eller AAA -batterier.Dess speciella design...på 1970/01/1 52184